#### Weak Persistency Semantics from the Ground Up:

Formalising the Persistency Semantics of ARMv8 & Transactional Models

#### Azalea Raad John Wickerson Viktor Vafeiadis

Max Planck Institute for Software Systems (MPI-SWS) Imperial College London

# Computer Storage

✓ fastX volatile

X slow √ persistent

# What is Non-Volatile Memory (NVM)?

#### NVM: Hybrid Storage + Memory

Best of both worlds:

- ✓ *persistent* (like HDD)

- √ fast, random access (like RAM)

# INTEL® OPTANETM TECHNOLOGY

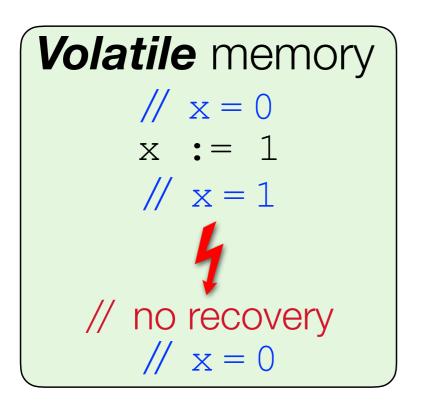

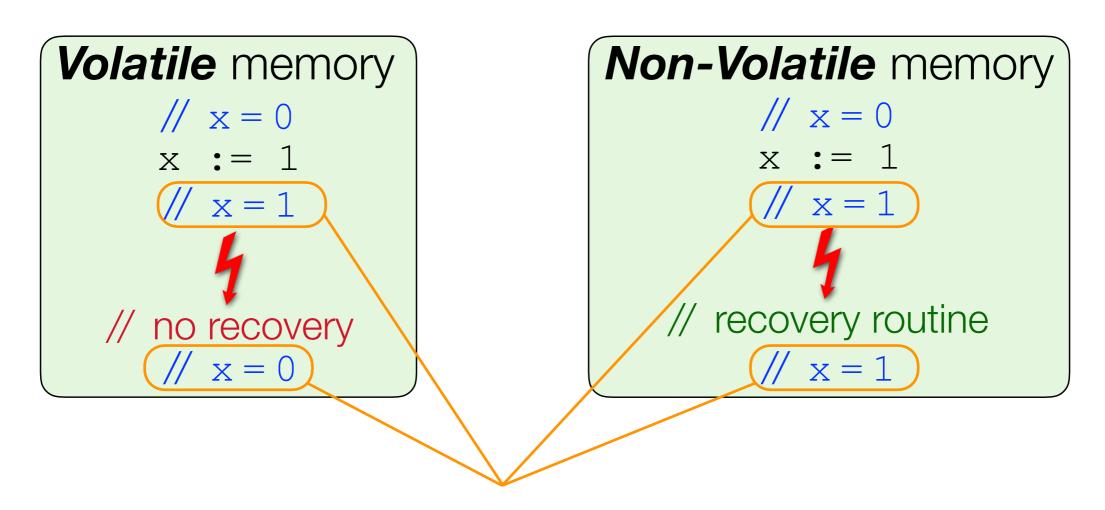

Non-Volatile memory // x = 0 x := 1 // x = 1 // x = 1 // recovery routine // x = 1

### A: Program Verification

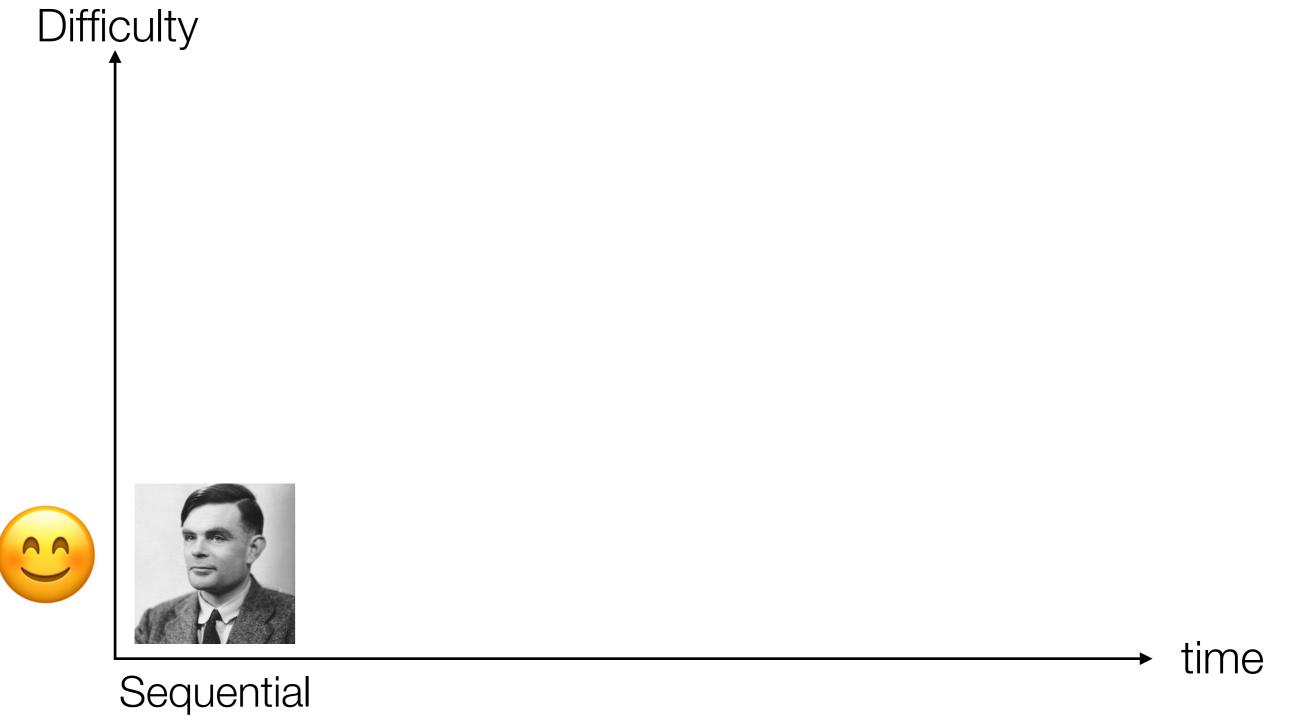

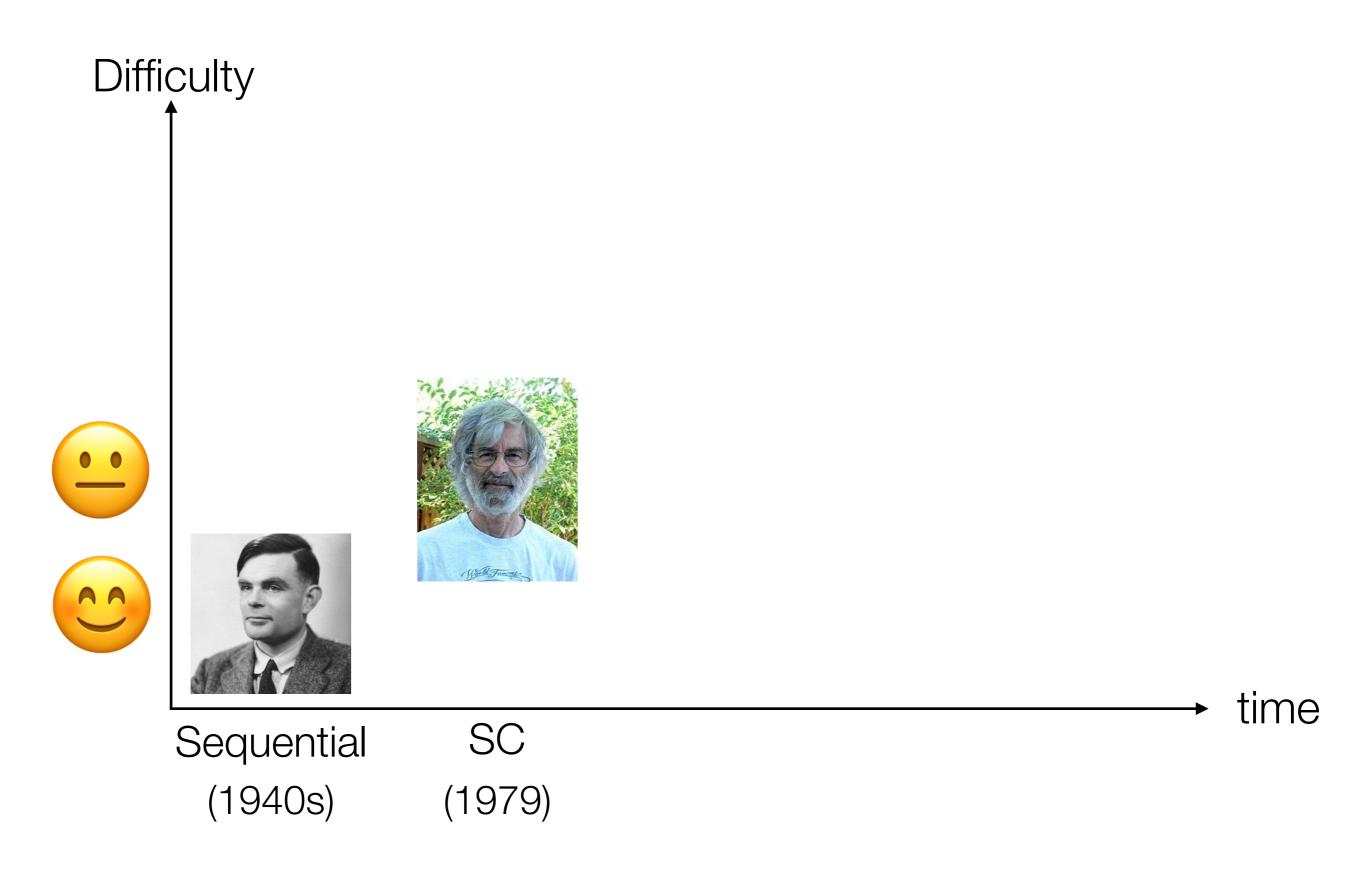

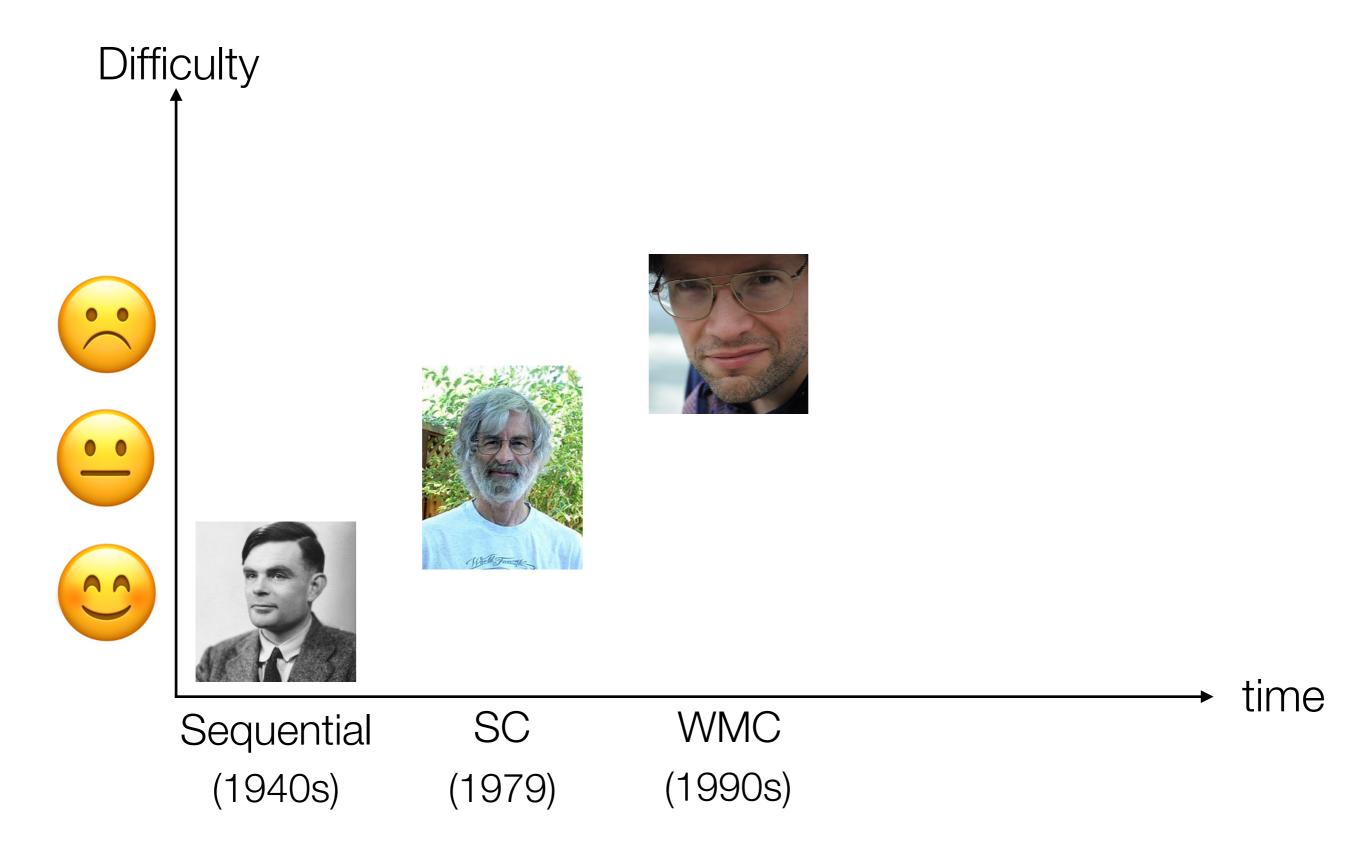

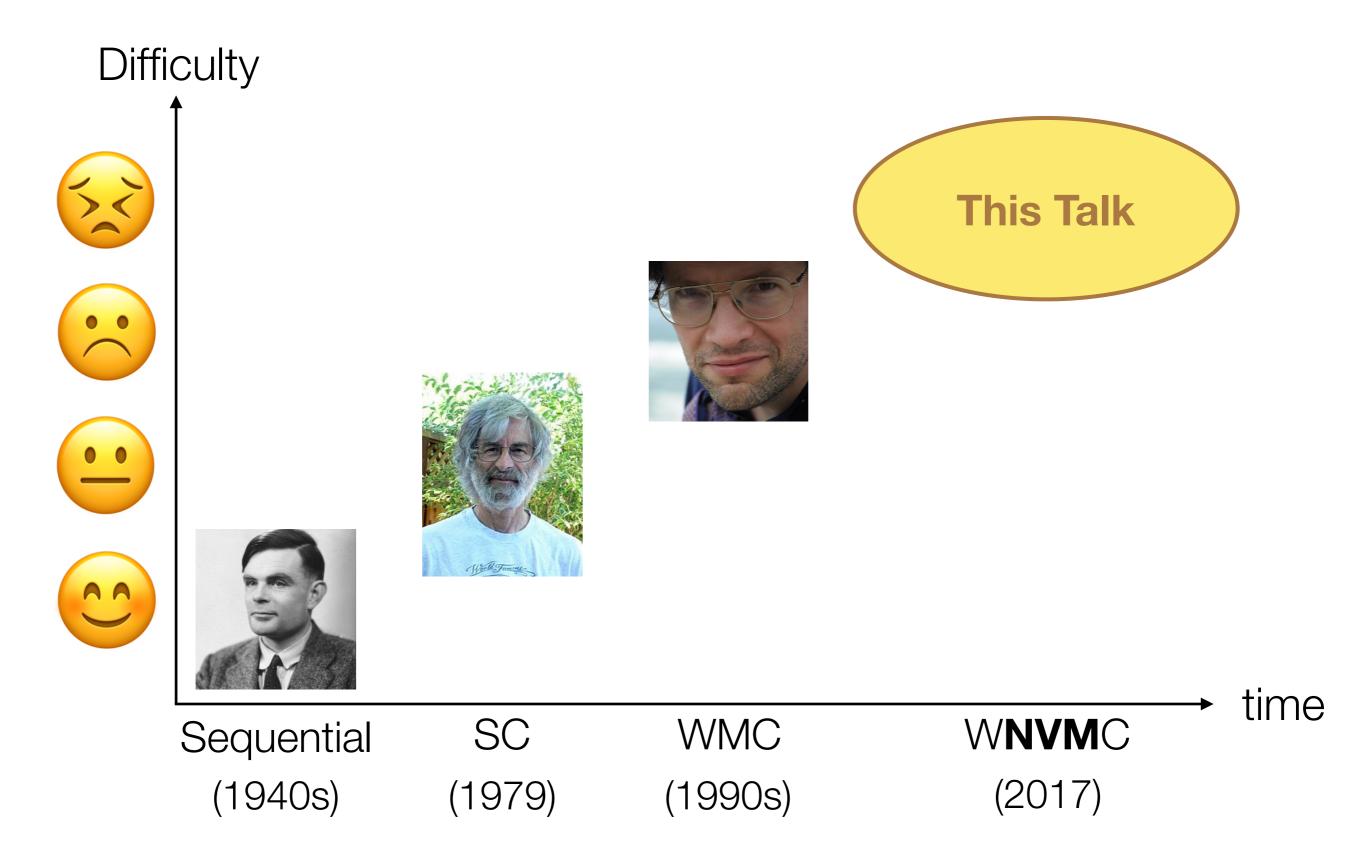

(1940s)

# Weak Memory Consistency (WMC)

**No** total execution order (*to*)  $\Rightarrow$

weak behaviour absent under SC, caused by:

- instruction *reordering* by compiler

- write propagation across *cache hierarchy*

# Weak Memory Consistency (WMC)

**No** total execution order (*to*)  $\Rightarrow$

e.g. TSO, ARMv8, POWER, C11, Java

**!!** Execution continues *ahead of persistence*

- asynchronous persists

- I Execution continues ahead of persistence — asynchronous persists

- !! Writes may persist out of order

- *relaxed* persists

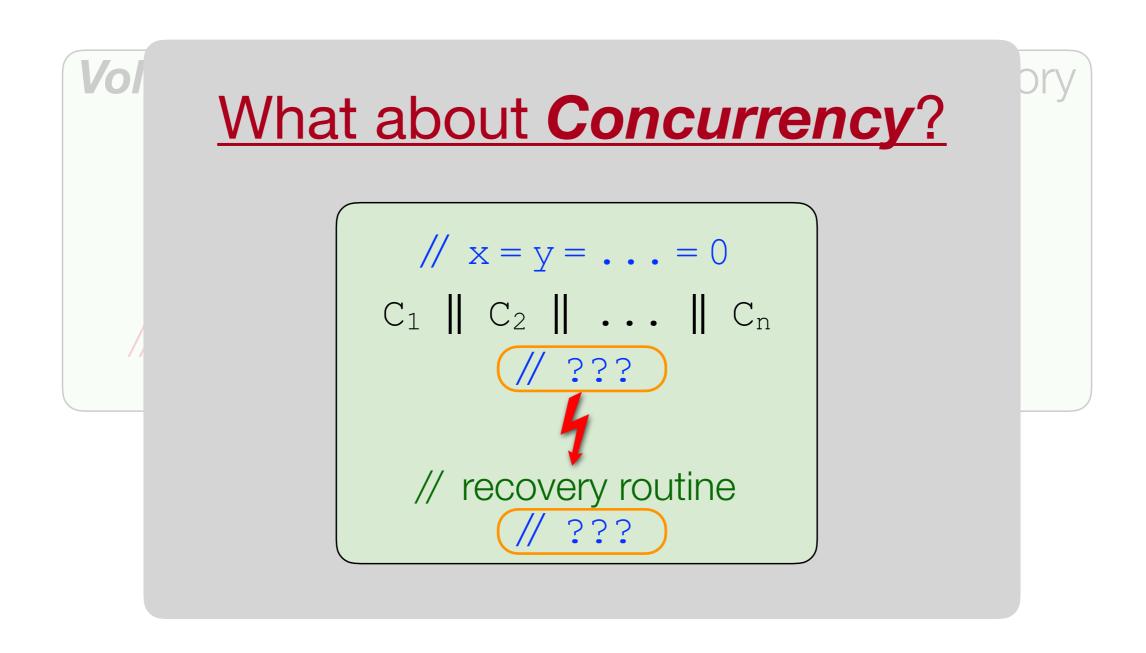

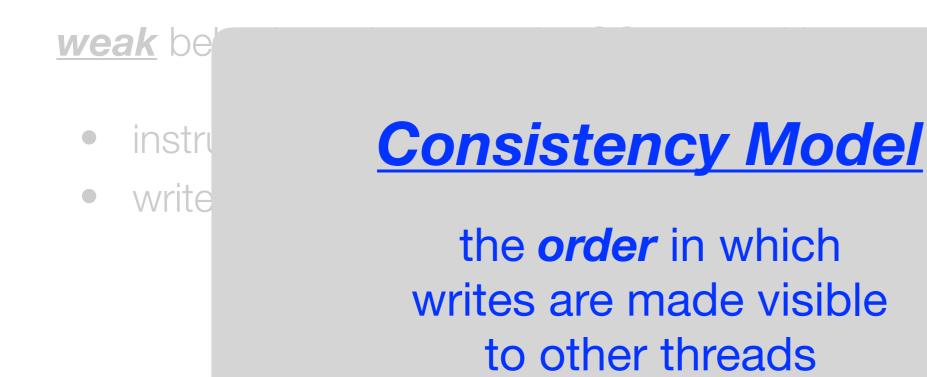

#### **Consistency Model**

the *order* in which writes are *made visible* to other threads

#### **Persistency Model**

the *order* in which writes are *persisted* to NVM

// x=

!! F

!! W

9

#### **Consistency Model**

the *order* in which writes are *made visible* to other threads

#### **Persistency Model**

the **order** in which writes are **persisted** to NVM

// x=

!! F

#### **NVM Semantics** Consistency + Persistency Model

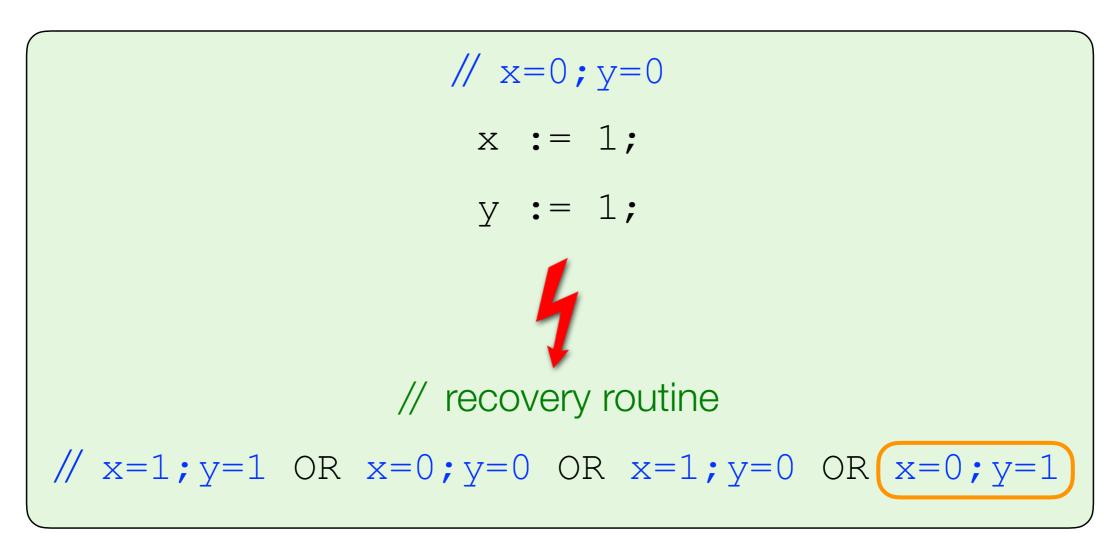

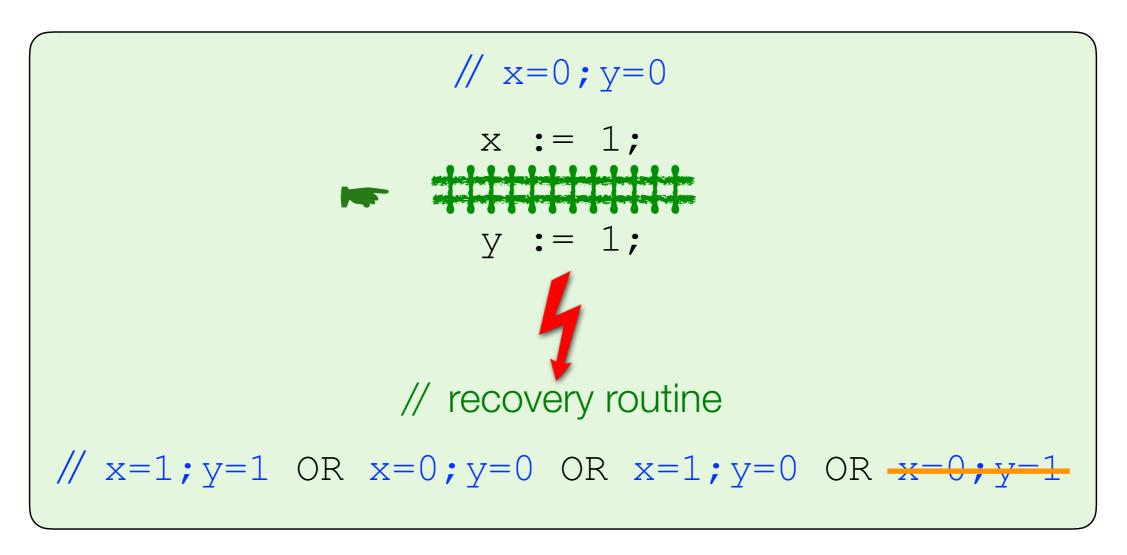

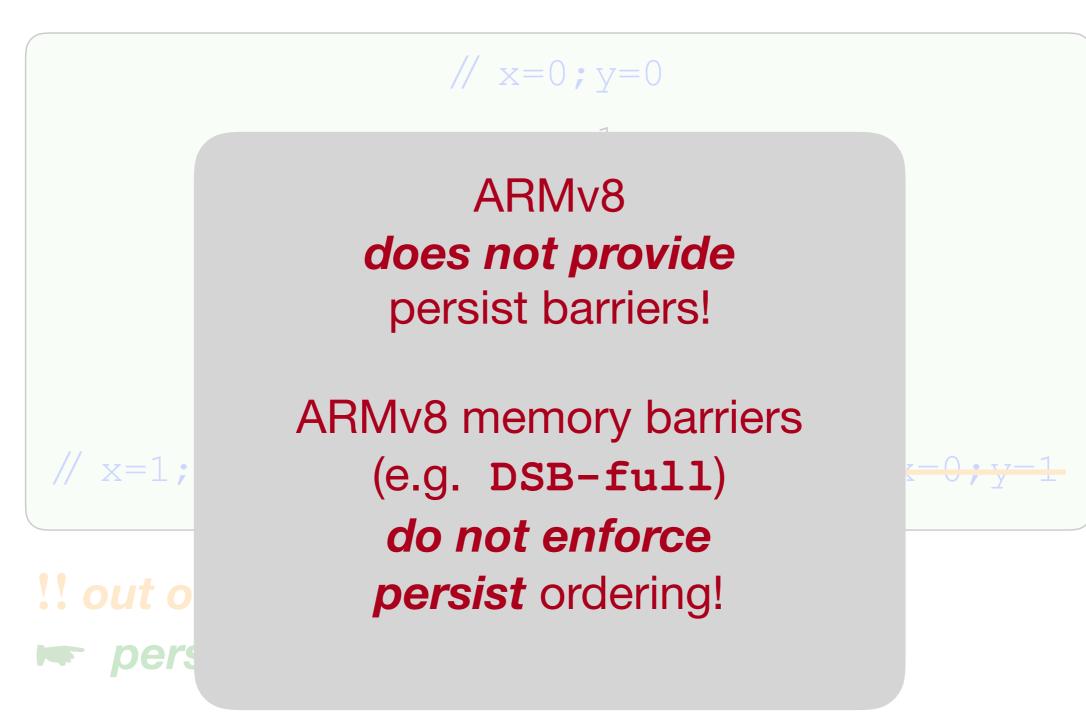

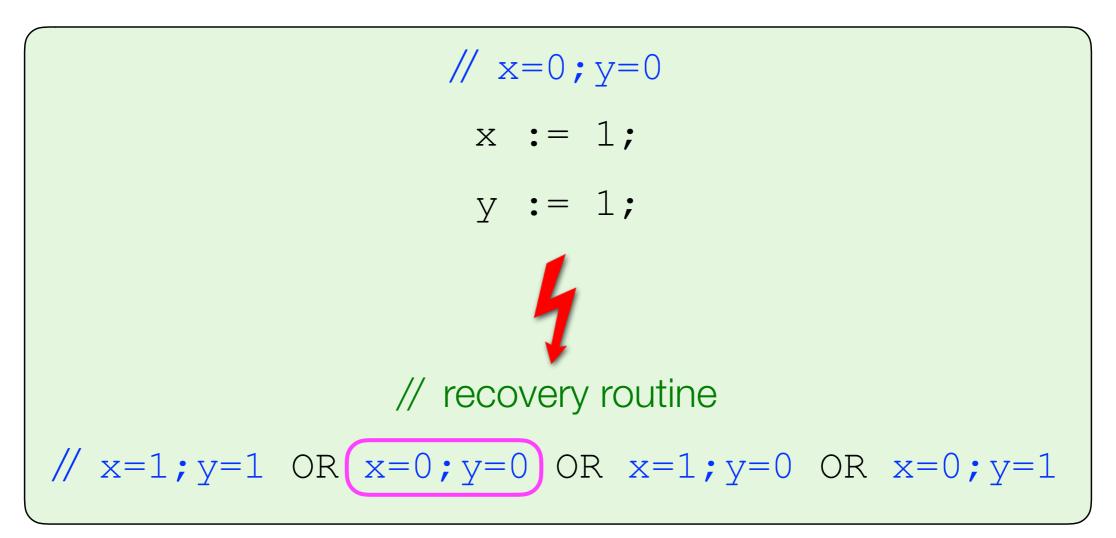

### Challenge #1: Relaxed Persists

#### **!! out of order persists**

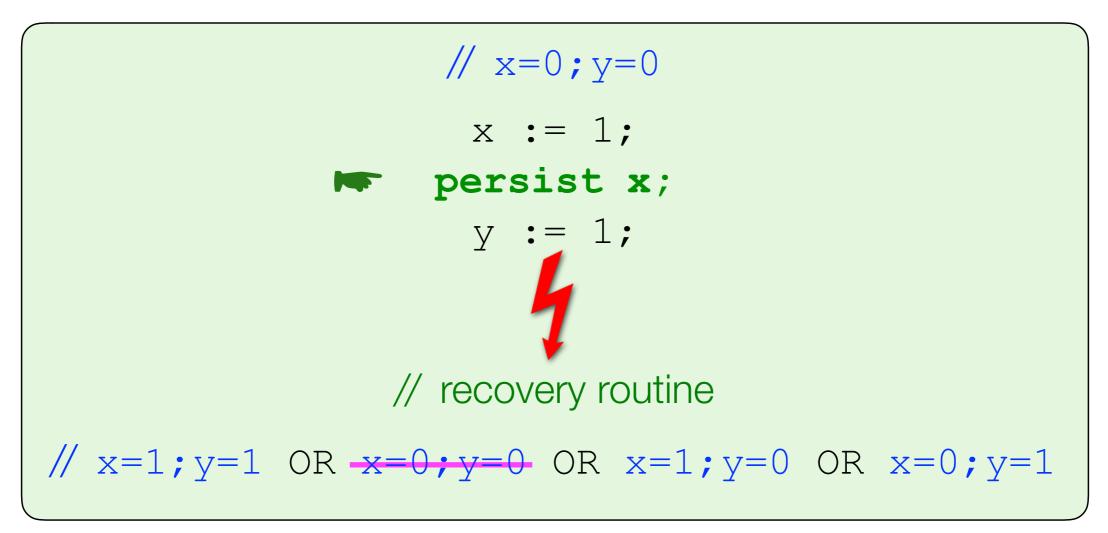

### Persist Barriers: Desiderata

!! out of order persists

persist barriers?

#### Persist Barriers: Desiderata

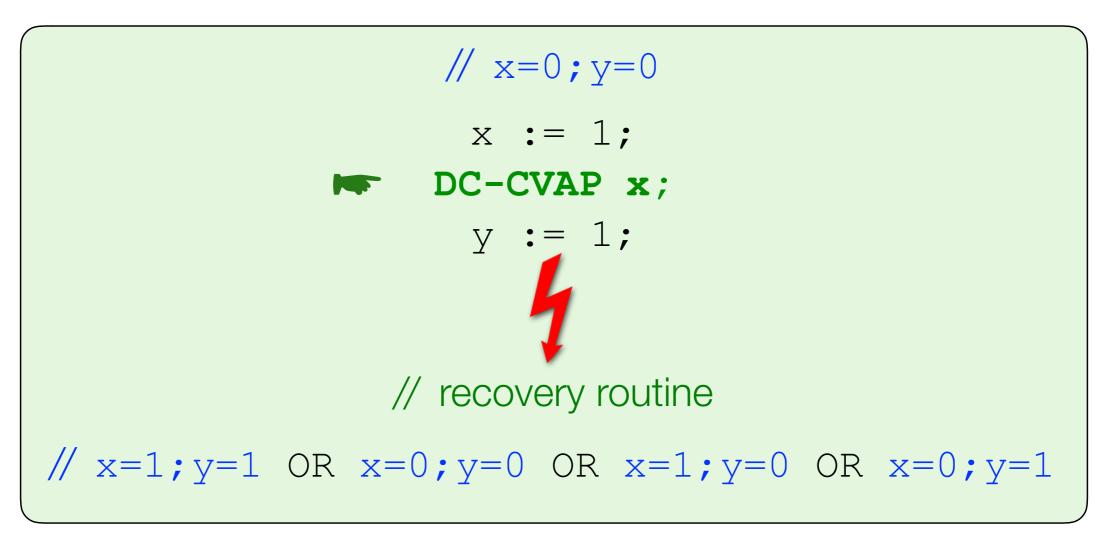

#### Challenge #2: Asynchronous Persists

**!!** Execution continues *ahead of persistence*

# Explicit Persists: Desiderata

**!!** Execution continues *ahead of persistence*

explicit persists?

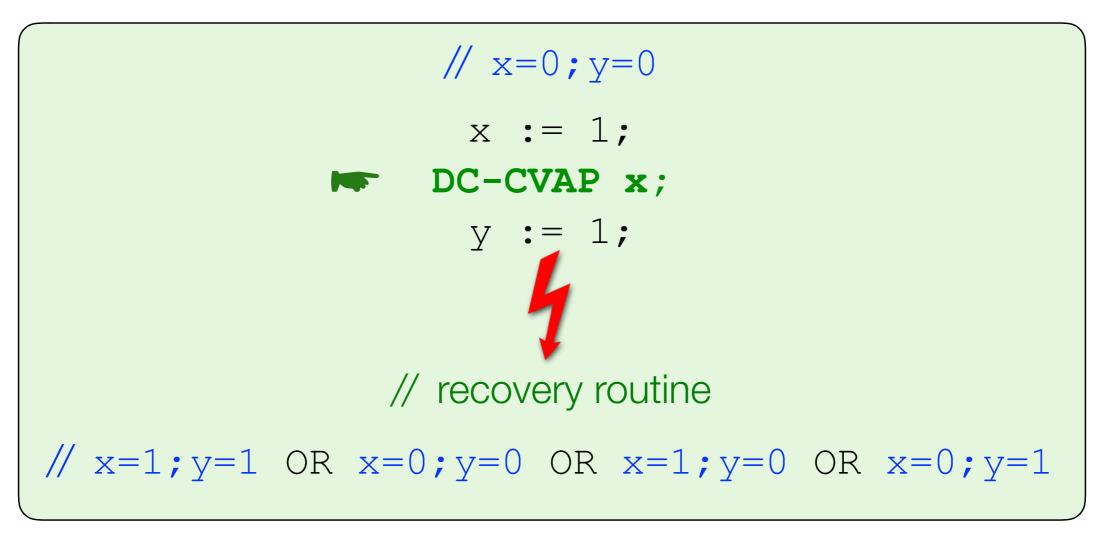

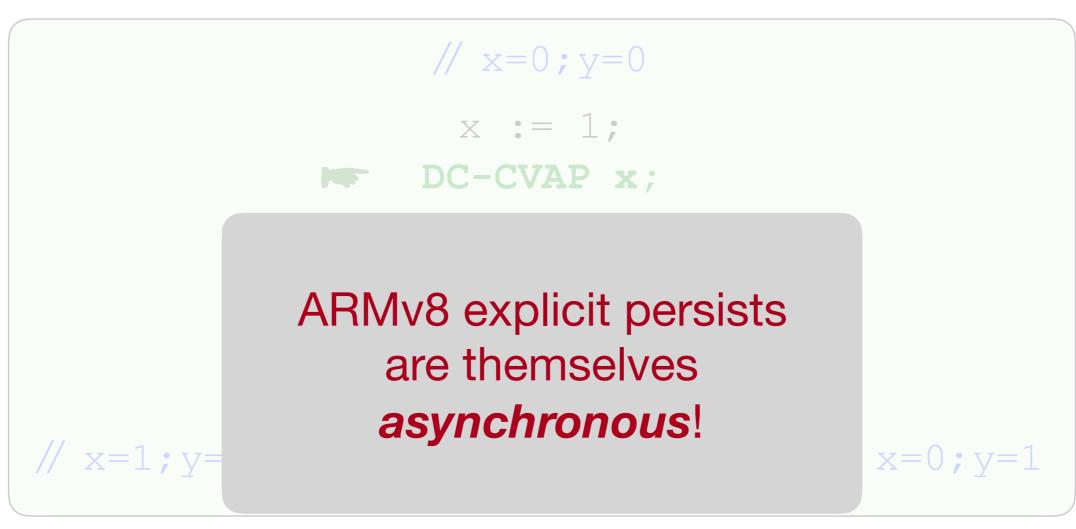

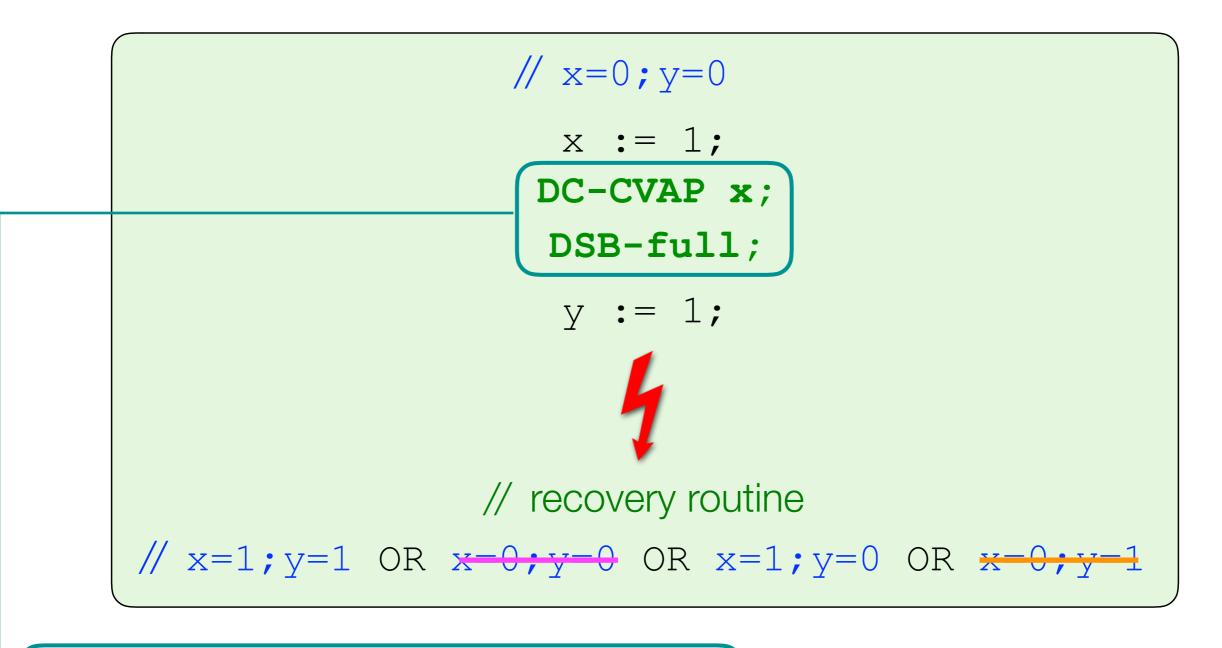

# Explicit Persists: Reality on ARMv8

**!!** Execution continues *ahead of persistence*

explicit persists?

# Explicit Persists: Reality on ARMv8

#### **!!** Execution continues *ahead of persistence*

#### explicit persists?

DC-CVAP x: asynchronously persist cache line containing x

# Explicit Persists: Reality on ARMv8

- **!!** Execution continues *ahead of persistence*

- explicit persists?

DC-CVAP x: asynchronously persist cache line containing x

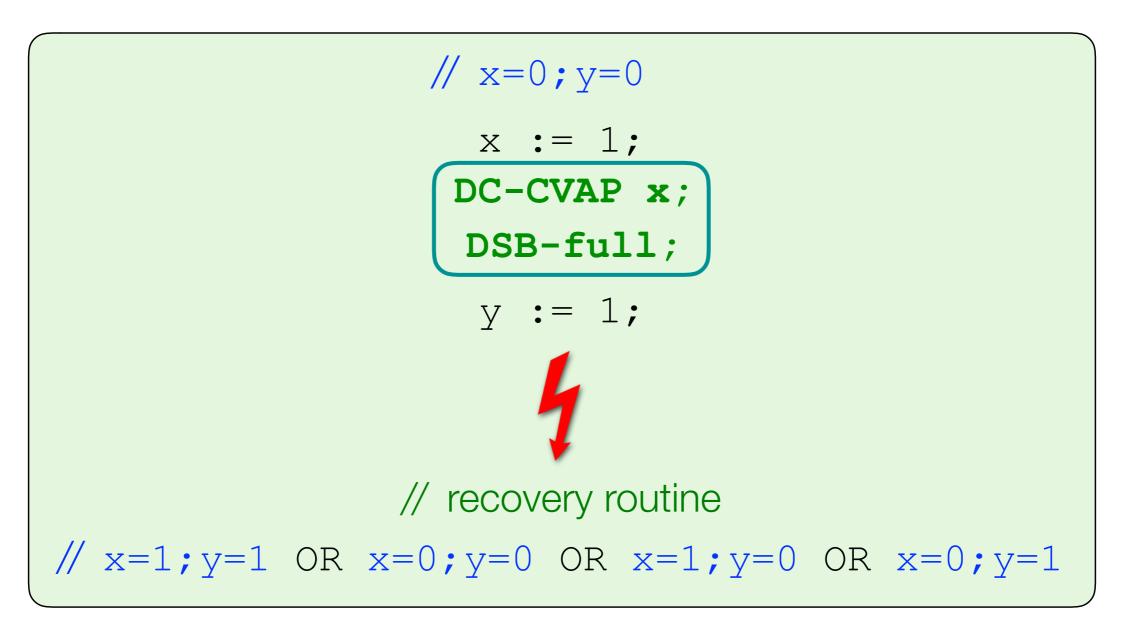

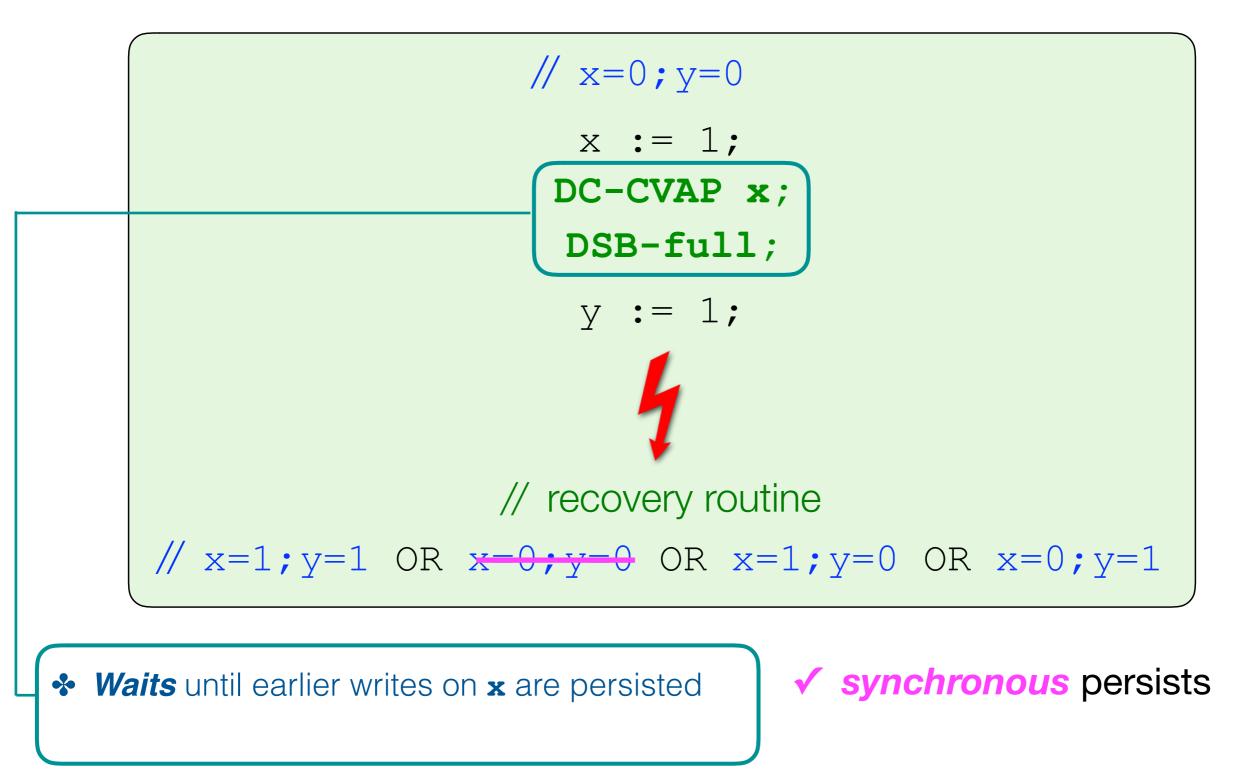

### Solution: Persist Sequence

### Solution: Persist Sequence

### Solution: Persist Sequence

Waits until earlier writes on x are persisted

Disallows reordering

✓ synchronous persists

✓ no out of order persists

#### ARM® Architecture Reference Manual

#### ARM® Architecture Reference Manual

- " a DSB-full will not complete until all previous DC-CVAP have completed "

- " **DC-CVAP** executes in program order relative to writes to an address in the same cache line"

#### ARM® Architecture Reference Manual

- " a DSB-full will not complete until all previous DC-CVAP have completed "

- " DC-CVAP executes in program order relative to writes to an address in the same cache line"

#### Ambiguities in text!

#### ARM® Architecture Reference Manual

- " a **DSB-full** will not complete until all previous **DC-CVAP** have completed "

- " **DC-CVAP** executes in program order relative to writes to an address in the same cache line"

#### Ambiguities in text!

#### PARMv8 Axiomatic Specification

- ARMv8 axioms in [Pulte et al. 2018] hold

- $(po^?; [DMB_{full} \cup DSB_{full}]; po^?) \setminus id \subseteq ob$

- $\forall X \in CL. [W_X \cup R_X]; po; [WB_X] \subseteq ob$

- $\forall X \in CL. [WB_X]; po; [WB_X] \subseteq ob$

- $dom([WB]; ob; [DSB_{full}]) \subseteq P$

- $[WB]; ob; [DSB_{full}]; ob; [D] \subseteq nvo$

- $\forall X \in \text{CL.} [W_{X_p}]; \text{ob}; [WB_{X_p}] \subseteq \text{nvo}$

- $\forall x_p \in \text{PLoc. } \mathbf{mo}_{x_p} \subseteq \mathbf{nvo}$

**ARM®** Archite

" a **DSB-full** all previous **D**

" DC-CVAP exe relative to wri same cache lii

#### **Problem**

*ambiguous* text *counter-intuitive* semantics *low-level* hardware details

#### **Solution**

*high-level, hardware-agnostic* NVM libraries:

**Persistent Transactions**

#### ification

al. 2018] hold o<sup>?</sup>) \ id  $\subseteq$  ob  $VB_X$ ]  $\subseteq$  ob  $\subseteq$  ob P  $\subseteq$  nvo  $\subseteq$  nvo

Ambiguities in text!

### What is a Transaction?

Concurrency control mechanism:

- *atomic* work unit:

- ➡ all-or-nothing writes

- consistent (e.g. serialisable)

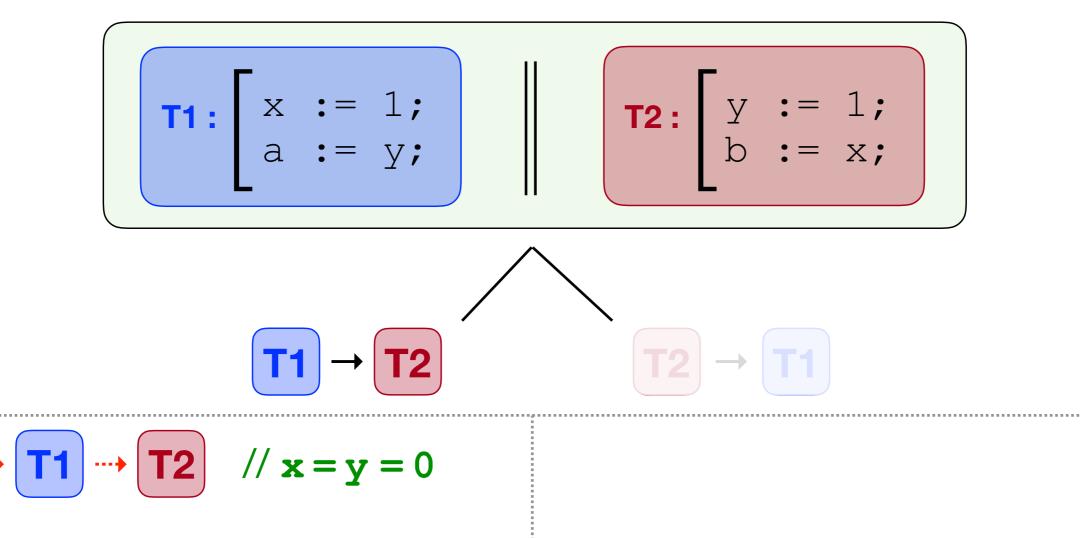

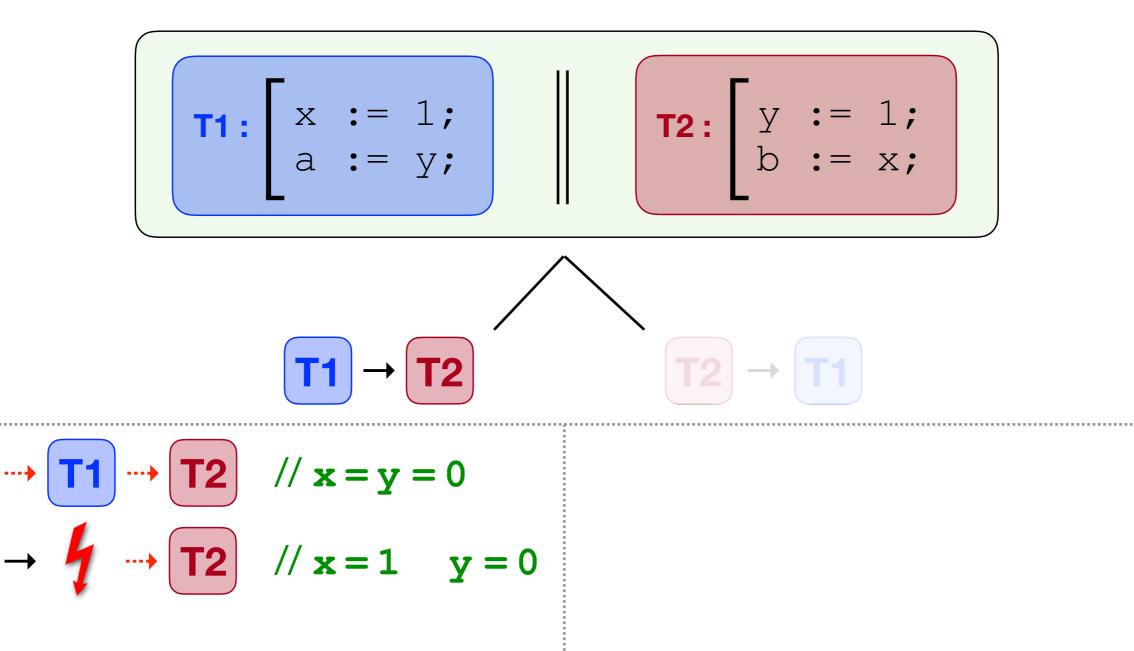

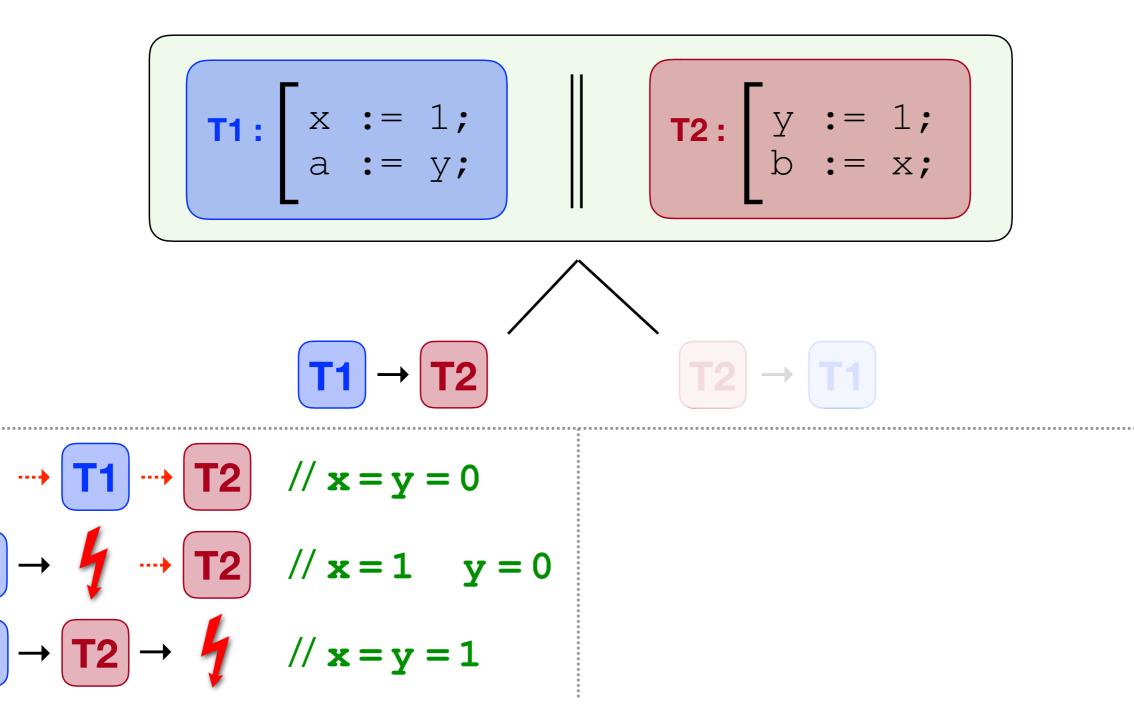

$$// x = y = 0$$

$$T: \begin{bmatrix} x := 1; \\ y := 1; \\ // x = y = 0 \quad OR \quad x = y = 1 \end{bmatrix}$$

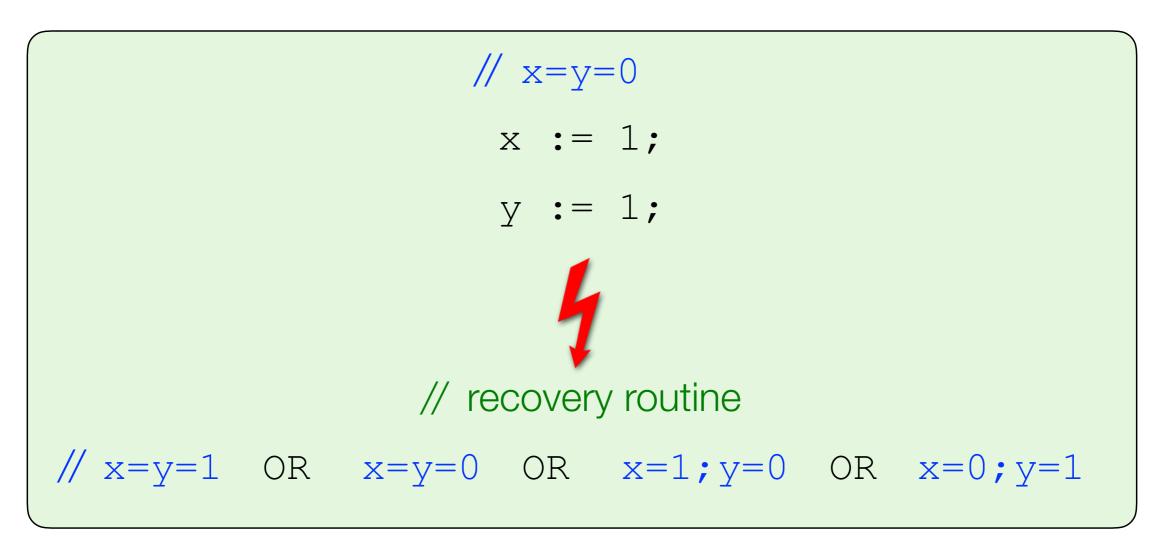

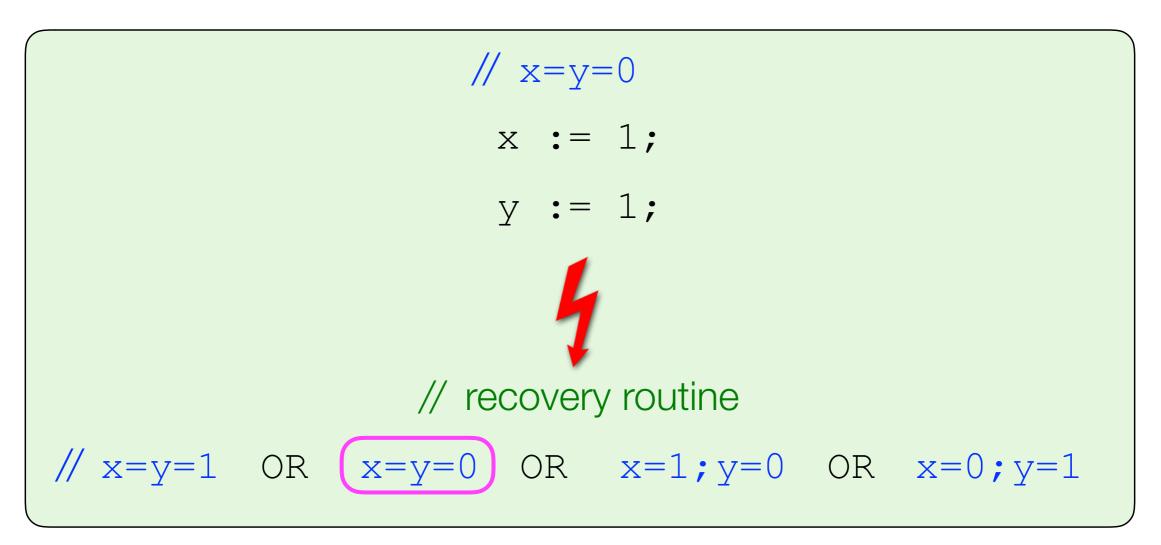

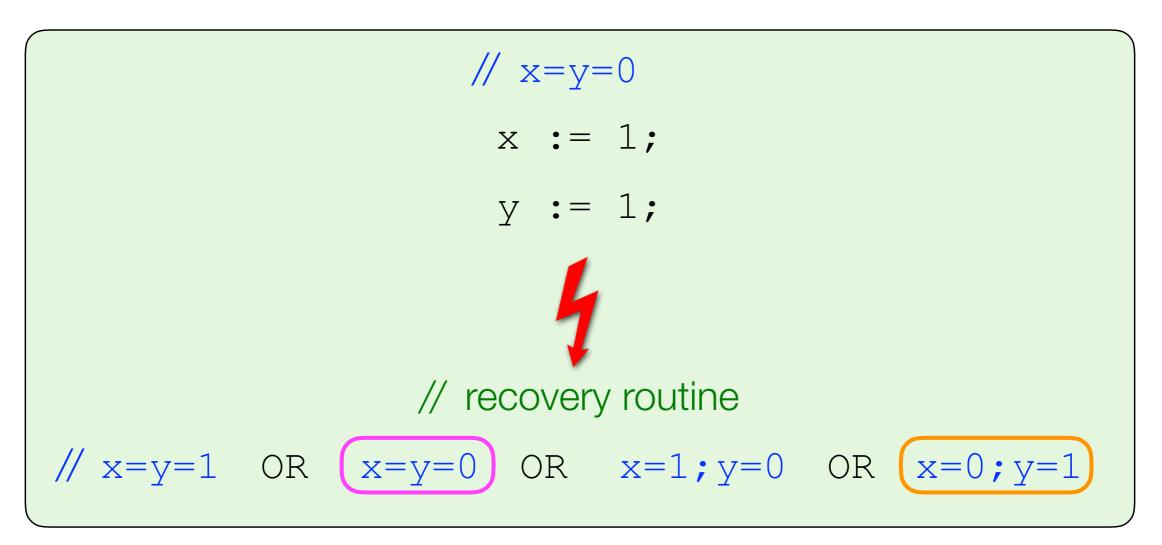

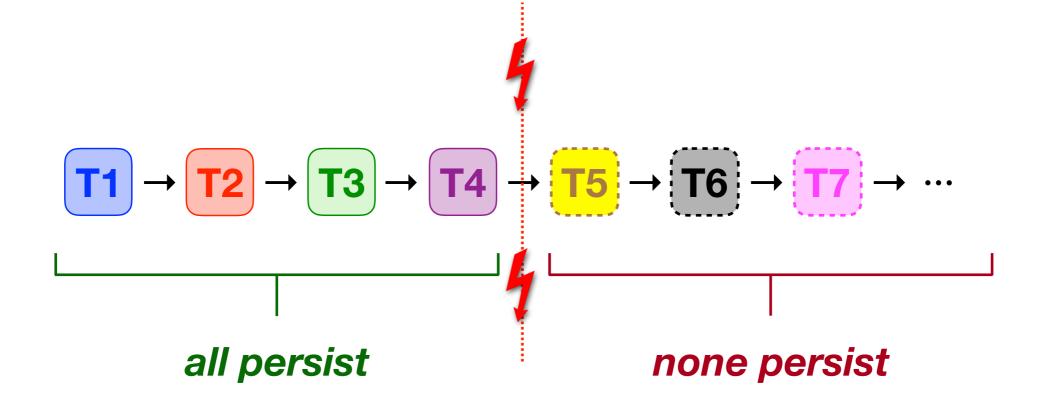

### What is a **Persistent** Transaction?

Concurrency & *persistency* control mechanism:

- *atomic* work unit:

- all-or-nothing writes

- → all-or-nothing *persists*

- consistent (e.g. serialisable)

$$\begin{array}{c} // x = y = 0 \\ \textbf{T}: \begin{bmatrix} x & := 1; \\ y & := 1; \\ \end{array} \\ // recovery routine \\ // x = y = 0 \quad \text{OR} \quad x = y = 1 \end{array}$$

### What is a **Persistent** Transaction?

Concurrency & *persistency* control mechanism:

- *atomic* work unit:

- all-or-nothing writes

- → all-or-nothing *persists*

- consistent (e.g. serialisable)

- persistent (e.g. persistently serialisable)

$$\begin{array}{c} // x = y = 0 \\ \textbf{T}: \begin{bmatrix} x & := 1; \\ y & := 1; \\ \end{array} \\ // recovery routine \\ // x = y = 0 \quad \text{OR} \quad x = y = 1 \end{array}$$

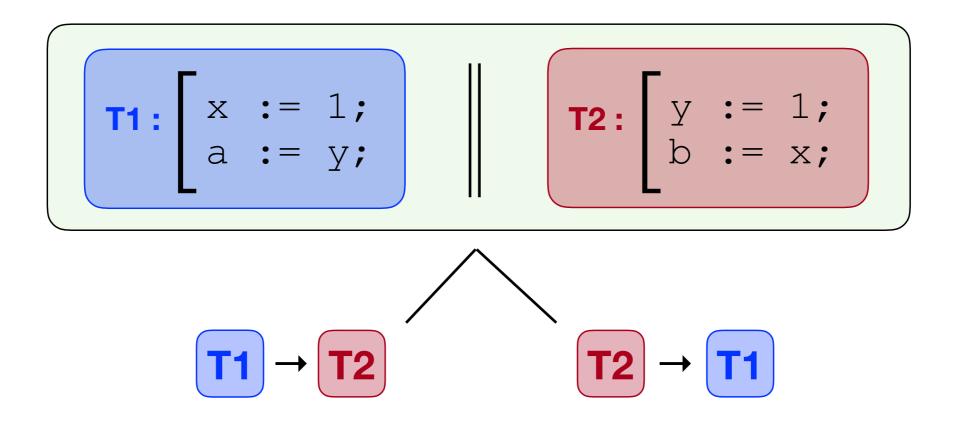

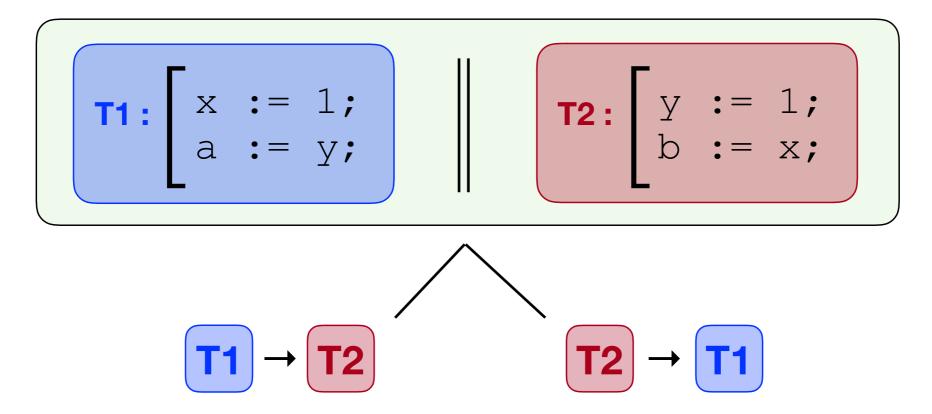

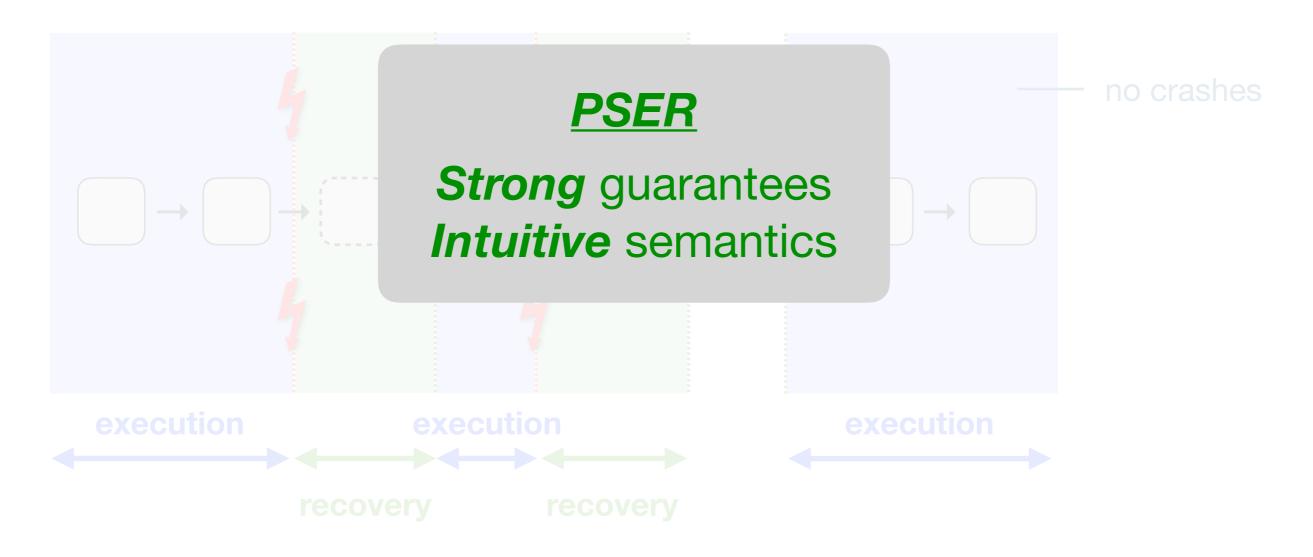

### Serialisability (SER)

All transactions appear to execute in a sequential order

All transactions appear to execute in a sequential order

All transactions appear to execute in a sequential order

All transactions appear to execute in a sequential order

All transactions appear to execute in a sequential order

All transactions appear to execute in a sequential order

All transactions appear to execute in a sequential order

A prefix of transactions appears to persist in the same sequential order

in <u>each era</u>

All transactions appear to execute in a sequential order

A prefix of transactions appears to persist in the same sequential order in <u>each era</u>

All transactions appear to execute in a sequential order

A prefix of transactions appears to persist in the same sequential order in <u>each era</u>

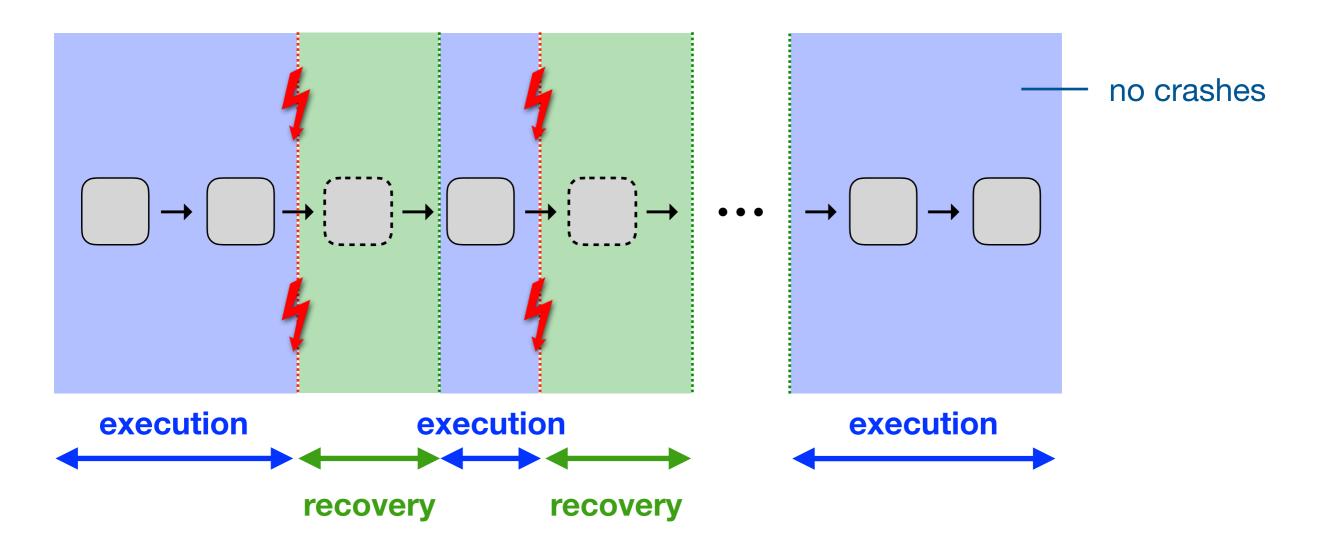

### Is PSER *Feasible*?

#### ✓ PSER *implementation* in *ARM*

Take **SER** Implementation — e.g. 2-PL

- ✤ add code for *persistence* i.e. persist sequences

- ✤ add code to *log metadata* for *recovery*

- + add recovery mechanism

## Is PSER *Feasible*?

#### ✓ PSER implementation in ARM

Take **SER** Implementation — e.g. 2-PL

- ✤ add code for *persistence* i.e. persist sequences

- + add code to *log metadata* for *recovery*

- + add *recovery mechanism*

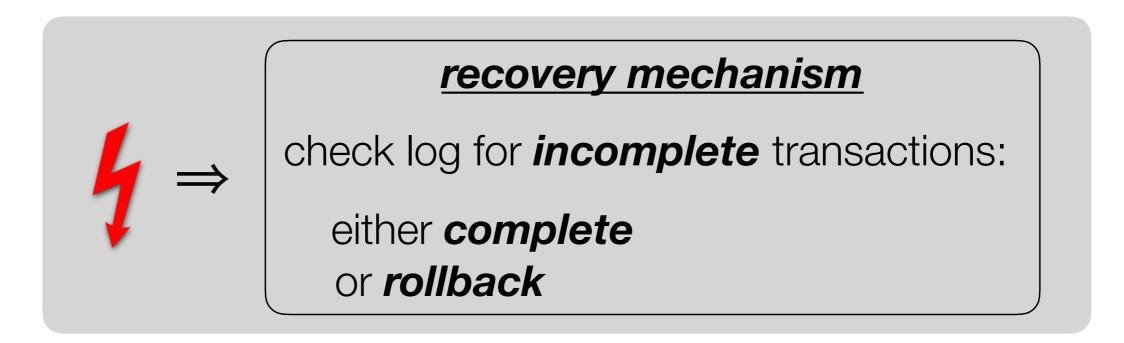

## Is PSER *Feasible*?

check log for *incomplete* transactions:

either **complete** or **rollback**

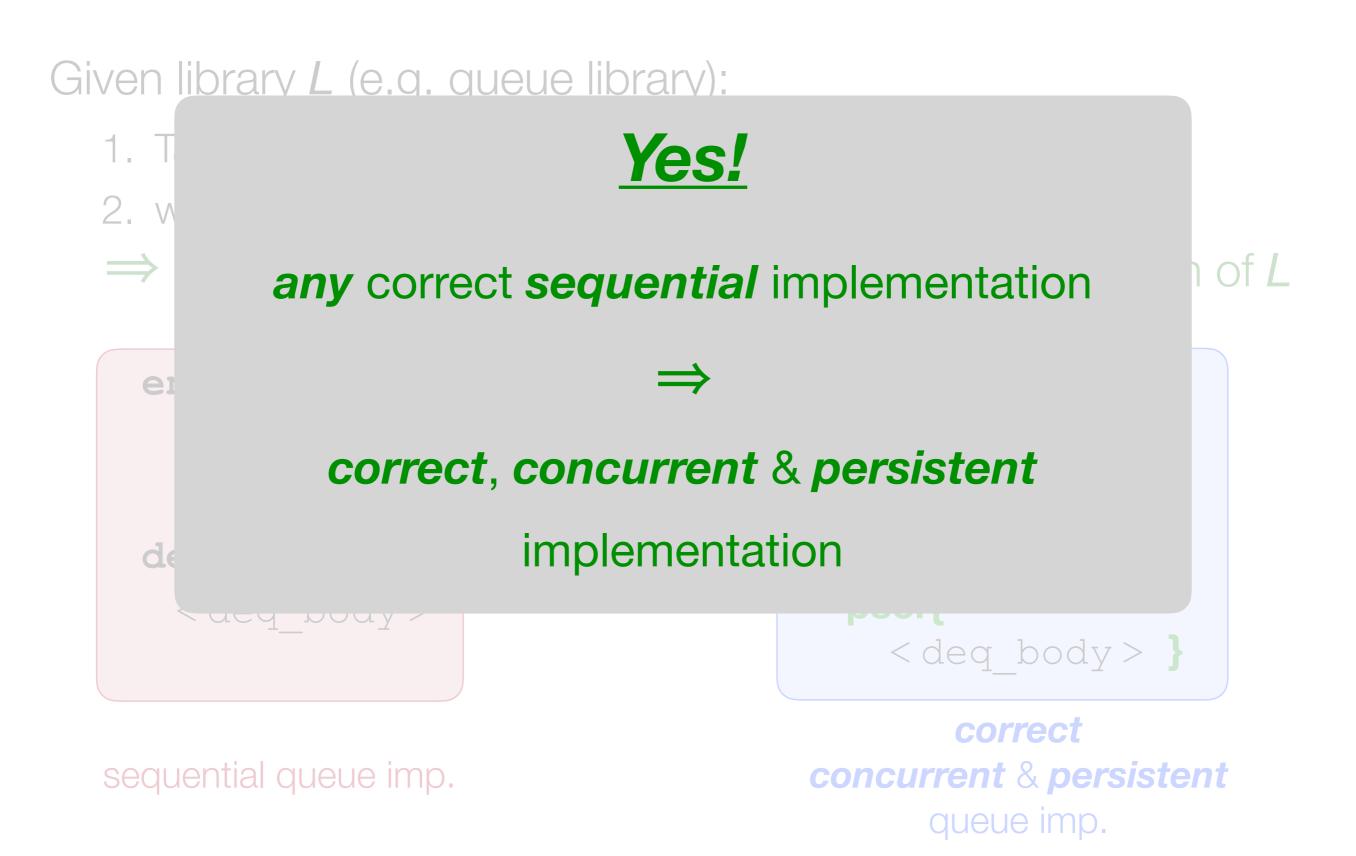

Given library *L* (e.g. queue library):

1. Take **any** correct **sequential** implementation of L

| <pre>enq(q,v) =   &lt; enq_body &gt;</pre> |

|--------------------------------------------|

| <b>deq(q)=</b><br><deq_body></deq_body>    |

sequential queue imp.

Given library *L* (e.g. queue library):

- 1. Take **any** correct **sequential** implementation of L

- 2. wrap each operation in a PSER transaction

| <b>enq(q,v)=</b><br><enq_body></enq_body> |

|-------------------------------------------|

| <b>deq(q)=</b><br><deq_body></deq_body>   |

sequential queue imp.

Given library *L* (e.g. queue library):

- 1. Take **any** correct **sequential** implementation of L

- 2. wrap each operation in a PSER transaction

⇒ correct, concurrent & persistent implementation of L

| <pre>enq(q,v) =   &lt; enq_body &gt;</pre> |                                          |

|--------------------------------------------|------------------------------------------|

| <b>deq(q)=</b><br><deq_body></deq_body>    |                                          |

|                                            | <pre><enq_body> deq(q)=</enq_body></pre> |

sequential queue imp.

enq(q,v) =pser{ <enq body> } deq(q) =pser{ <deq body> }

*correct concurrent* & *persistent* queue imp.

### Summary

- ✓ Formalised architecture-level NVM semantics:

✤ PARMv8

- ✓ Formalised *language-level* NVM semantics:

✤ PSER

- ✓ More in the paper

- ✤ General framework for declarative persistency

- **?** Future Work:

- ✤ program logics

- model checking algorithms

### Summary

- ✓ Formalised architecture-level NVM semantics:

✤ PARMv8

- ✓ Formalised *language-level* NVM semantics:

✤ PSER

- ✓ More in the paper

- ✤ General framework for declarative persistency

- **?** Future Work:

- ✤ program logics

- model checking algorithms

### Thank You for Listening!

azalea@mpi-sws.org