Formalizing the Concurrency Semantics of an LLVM Fragment

#### Soham Chakraborty, Viktor Vafeiadis

Max Planck Institute for Software Systems (MPI-SWS)

CGO 2017

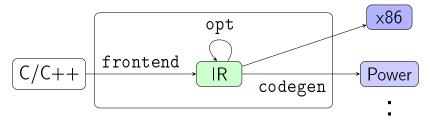

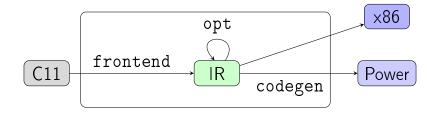

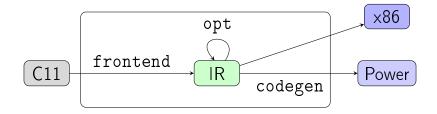

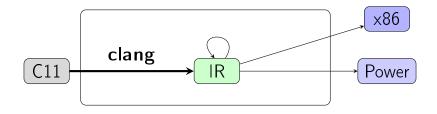

### LLVM Compilation

LLVM

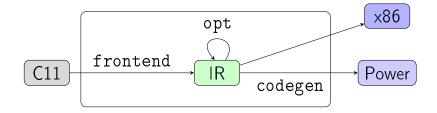

### LLVM Concurrency Compilation

### LLVM Concurrency Compilation

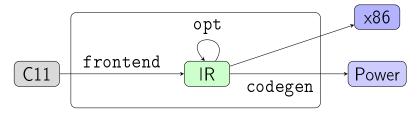

formalized

formalized

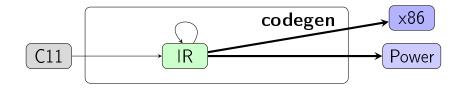

### LLVM Concurrency Compilation

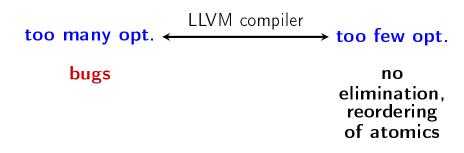

Correctness of the transformations is unclear

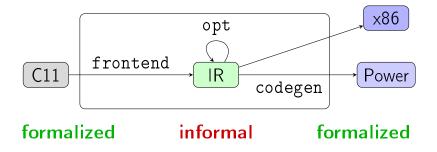

Limitation of LLVM Informal Concurrency

Valid opt is removed by over-restriction in bug fix

formalized informal formalized

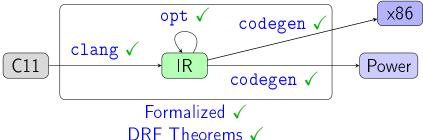

Formalized fragment of LLVM concurrency (except monotonic/relaxed accesses and fences)

Proved correctness of transformations

Informal text in Language Reference Manual

Frequent references to C11 concurrency

- "This model is inspired by the C++0x memory model."

- "These semantics are borrowed from Java and C++0x, but are somewhat more colloquial."

- This is intended to match shared variables in  $C/C++\ldots$ "

## Why not adopt C11 concurrency?

Subtle differences

- A program has write-read race on non-atomics

- C11: the behavior of the program is *undefined*

- LLVM: *defined* behavior;

\* racy read returns **undef(u)**

$$X = 1; \quad \begin{vmatrix} \text{if}(X) \\ t = 4; \\ \text{else} \\ t = 4; \\ t \neq 4 ? : \quad \text{C11} \checkmark \quad \text{LLVM} \checkmark$$

- Set of allowed optimizations are different

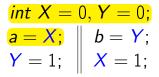

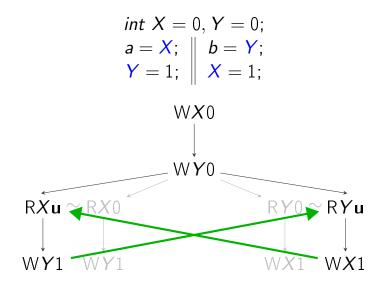

### Formalization by Event Structure

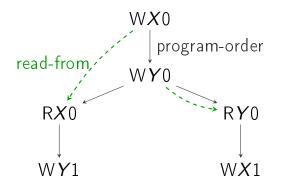

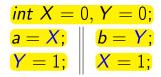

- Program

int

$$X = 0, Y = 0;$$

$a = X; \| b = Y;$

$Y = 1; \| X = 1;$

- Event Structure

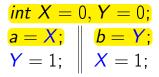

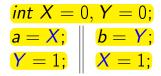

$$\begin{array}{c|c} int \ X = 0, \ Y = 0; \\ a = X; \\ Y = 1; \end{array} \begin{array}{c} b = Y; \\ X = 1; \end{array}$$

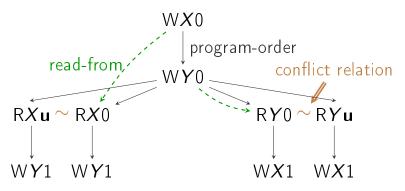

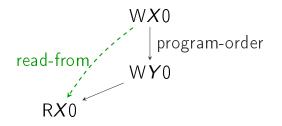

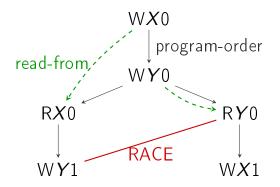

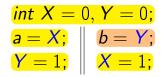

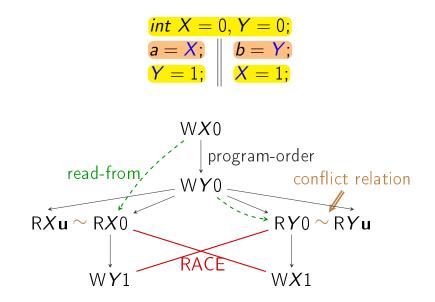

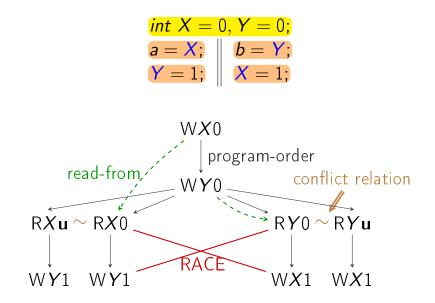

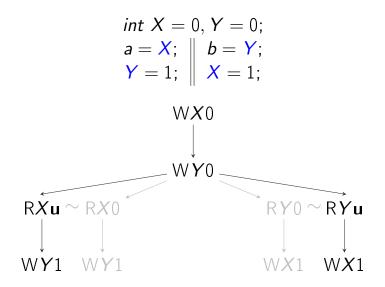

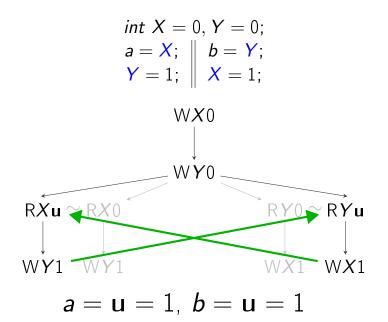

# Program Behavior

int

$$X = 0, Y = 0;$$

$a = X; \| b = Y;$

$Y = 1; \| X = 1;$

$a = b = 1?$

# Program Behavior

int

$$X = 0, Y = 0;$$

$a = X; \| b = Y;$

$Y = 1; \| X = 1;$

$a = b = 1? \checkmark$

$$int X = 0, Y = 0; \qquad int X = 0, Y = 0; \begin{pmatrix} a = X; \\ Y = 1; \end{pmatrix} b = Y; \qquad Y = 1; \\ X = 1; \end{pmatrix} \sim Y = 1; \\ a = X; \\ b = Y; \end{pmatrix} A = 1;$$

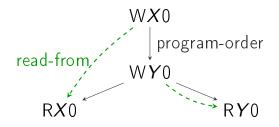

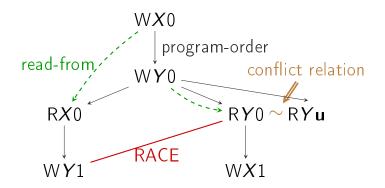

#### Execution from Event Structure

#### Execution from Event Structure

#### Execution from Event Structure

- Proposed formalization handles

- Memory operations: load, store, CAS

- Memory orders: non-atomic, acquire, release, acquire\_release, sequentially consistent (SC)

- Preserves *consistency* at each construction step

- Multiple consistent event structures per program

## Transformation Correctness

# Behavior $(P_{tgt}) \subseteq$ Behavior $(P_{src})$ Behavior. final values observed in each location

## Transformation Correctness

# Behavior $(P_{tgt}) \subseteq$ Behavior $(P_{src})$ Behavior. final values observed in each location

$Behavior(G_{tgt}) \subseteq Behavior(G_{src})$

♠

## LLVM performs these eliminations

Adjacent read after read/write elimination

•

$$a = X_o; b = X_{na}; \rightsquigarrow a = X_o; b = a;$$

•  $X_o = v; b = X_{na}; \rightsquigarrow X_o = v; b = v;$

Adjacent overwritten write elimination

•

$$X_{na} = v'; X_{na} = v; \rightsquigarrow X_{na} = v;$$

Non-adjacent overwritten write elimination

### LLVM does NOT perform these eliminations

Adjacent read after read/write elimination

•  $a = X_{acq}; b = X_{acq}; \Rightarrow a = X_{acq}; b = a;$ •  $a = X_{sc}; b = X_{(acq|sc)}; \Rightarrow a = X_{sc}; b = a;$ •  $X_{rel} = v; b = X_{acq}; \Rightarrow X_{rel} = v; b = v;$ •  $X_{sc} = v; b = X_{(acq|sc)}; \Rightarrow X_{sc} = v; b = v;$

Adjacent overwritten write elimination

•

$$X_{rel} = v'; X_{rel} = v; \rightsquigarrow X_{rel} = v;$$

•  $X_{(rel|sc)} = v'; X_{sc} = v; \rightsquigarrow X_{sc} = v;$

## LLVM does NOT perform these eliminations

Adjacent read after read/write elimination

•

$$a = X_{acq}; b = X_{acq}; \Rightarrow a = X_{acq}; b = a;$$

•  $a = X_{sc}; b = X_{(acq|sc)}; \Rightarrow a = X_{sc}; b = a;$

•  $X_{rel} = v; b = X_{acq}; \Rightarrow X_{rel} = v; b = v;$

•  $X_{sc} = v; b = X_{(acq|sc)}; \Rightarrow X_{sc} = v; b = v;$

diagonal event events alimination

Adjacent overwritten write elimination

•

$$X_{rel} = v'; X_{rel} = v; \rightsquigarrow X_{rel} = v;$$

•  $X_{(rel|sc)} = v'; X_{sc} = v; \rightsquigarrow X_{sc} = v;$

Non-adjacent read after write elimination

# LLVM performs( $\checkmark$ ) these reorderings

| a; b $\rightsquigarrow$ b; a           |                |            |              |              |                     |

|----------------------------------------|----------------|------------|--------------|--------------|---------------------|

| $\downarrow a \setminus b \rightarrow$ | $(St Ld)_{na}$ | $St_{rel}$ | $Ld_{acq}$   | $Ld_{sc}$    | $U_{(acq\_rel sc)}$ |

| (St Ld) <sub>na</sub>                  | $\checkmark$   | -          | $\checkmark$ | $\checkmark$ | -                   |

| St <sub>rel</sub>                      | $\checkmark$   | -          | -            | -            | -                   |

| St <sub>sc</sub>                       | $\checkmark$   | -          | _            | -            | -                   |

| Ld <sub>acq</sub>                      | -              | -          | -            | -            | -                   |

| $U_{(acq_{rel} sc)}$                   | -              | -          | -            | -            | -                   |

$$X_{\text{rel}} = v; Y_{\text{na}} = v'; \rightsquigarrow Y_{\text{na}} = v'; X_{\text{rel}} = v; \quad \checkmark$$

# LLVM restricts( $\times$ ) these reorderings

| a; b $\rightsquigarrow$ b; a           |                |            |              |              |                     |

|----------------------------------------|----------------|------------|--------------|--------------|---------------------|

| $\downarrow a \setminus b \rightarrow$ | $(St Ld)_{na}$ | $St_{rel}$ | $Ld_{acq}$   | $Ld_{sc}$    | $U_{(acq\_rel sc)}$ |

| (St Ld) <sub>na</sub>                  | $\checkmark$   | ×          | $\checkmark$ | $\checkmark$ | ×                   |

| St <sub>rel</sub>                      | $\checkmark$   | ×          | -            | _            | ×                   |

| St <sub>sc</sub>                       | $\checkmark$   | ×          | -            | ×            | ×                   |

| Ld <sub>acq</sub>                      | ×              | ×          | ×            | ×            | ×                   |

| $U_{(acq_{rel} sc)}$                   | ×              | ×          | ×            | ×            | ×                   |

$$Y_{na} = v'; X_{rel} = v; \rightsquigarrow X_{rel} = v; Y_{na} = v'; \quad \times$$

# LLVM does NOT perform these reorderings

| a; b $\rightsquigarrow$ b; a           |                       |            |              |              |                     |

|----------------------------------------|-----------------------|------------|--------------|--------------|---------------------|

| $\downarrow a \setminus b \rightarrow$ | (St Ld) <sub>na</sub> | $St_{rel}$ | $Ld_{acq}$   | $Ld_{sc}$    | $U_{(acq\_rel sc)}$ |

| (St Ld) <sub>na</sub>                  | $\checkmark$          | ×          | $\checkmark$ | $\checkmark$ | ×                   |

| St <sub>rel</sub>                      | $\checkmark$          | ×          | $\checkmark$ | $\checkmark$ | ×                   |

| St <sub>sc</sub>                       | $\checkmark$          | ×          | $\checkmark$ | ×            | ×                   |

| Ld <sub>acq</sub>                      | ×                     | ×          | ×            | ×            | ×                   |

| $U_{(acq_{rel} sc)}$                   | ×                     | ×          | ×            | ×            | ×                   |

$$X_{

m rel} = v; t = Y_{

m acq}; \rightsquigarrow t = Y_{

m acq}; X_{

m rel} = v; \quad \checkmark$$

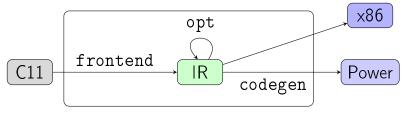

### C11 to LLVM Mapping Correctness

- LLVM has operations (Ld/St/CAS) and memory orders (na/rel/acq/acq\_rel/SC) similar to C11.

- LLVM model is stronger than C11.

### LLVM to Architecture Mapping Correctness

(LLVM  $\rightsquigarrow x86/Power$ ) = (C11  $\rightsquigarrow x86/Power$ ) Proved correctness of these mappings

- $\bullet$  LLVM to SC

- LLVM to SPower

Ensure correctness of LLVM  $\rightarrow \times 86/Power$  (results from Lahav & Vafeiadis. FM'16)

### What's More in The Paper

#### Event structure construction rules

Consistency constraints

$isCons(G) \triangleq irreflexive(wb) \land irreflexive(cf; hb)$  $\land irreflexive(rf; hb^{-1}; rf^{-1}; cf)$  $\land acyclic((hbsc \cup wb \cup fr); [SC])$

Consistency constraints

Data race freedom (DRF) theorems

Consistency constraints

Data race freedom (DRF) theorems

More transformations

- Speculative load

- Strengthening memory order of accesses

Consistency constraints

Data race freedom (DRF) theorems

More transformations

- Speculative load

- Strengthening memory order of accesses

Proofs: http://plv.mpi-sws.org/llvmcs/

# Conclusions & Future Directions

- Contributions

- Future: extend the LLVM concurrency model

- With relaxed accesses and fences

- Prove/disprove more optimizations

- Mechanize the formalization

# Thank You !

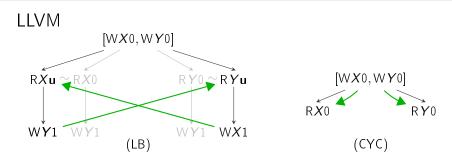

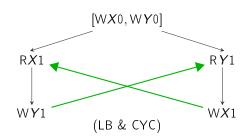

Examples

int

$$X = 0, Y = 0;$$

$a = X; \| b = Y;$

$Y = 1; \| X = 1;$

$a = b = 1 \checkmark$

(LB)

int

$$X = 0, Y = 0;$$

$a = X;$

$if(a == 1)$

$Y = 1;$

$a = b = 1$

$X = 1;$

$(CYC)$

### LLVM vs C11

C11

# LLVM performs speculative load

$$X = 1; \quad \begin{cases} \text{if}(flag) \{ \\ a = X; \\ \end{cases} \quad \Rightarrow \quad X = 1; \\ \end{cases} \quad \begin{cases} t = X; // \text{ undef} \\ \text{if}(flag) \{ \\ a = t; \\ \end{cases}$$