# Bridging the Gap between Programming Languages and Hardware Weak Memory Models

ANTON PODKOPAEV, St. Petersburg University, JetBrains Research, Russia, and MPI-SWS, Germany ORI LAHAV, Tel Aviv University, Israel VIKTOR VAFEIADIS, MPI-SWS, Germany

We develop a new intermediate weak memory model, IMM, as a way of modularizing the proofs of correctness of compilation from concurrent programming languages with weak memory consistency semantics to mainstream multi-core architectures, such as POWER and ARM. We use IMM to prove the correctness of compilation from the promising semantics of Kang et al. to POWER (thereby correcting and improving their result) and ARMv7, as well as to the recently revised ARMv8 model. Our results are mechanized in Coq, and to the best of our knowledge, these are the first machine-verified compilation correctness results for models that are weaker than x86-TSO.

Additional Key Words and Phrases: Weak memory consistency, IMM, promising semantics, C11 memory model

#### **ACM Reference Format:**

Anton Podkopaev, Ori Lahav, and Viktor Vafeiadis. 2019. Bridging the Gap between Programming Languages and Hardware Weak Memory Models. *Proc. ACM Program. Lang.* 3, POPL, Article 69 (January 2019), 36 pages. https://doi.org/10.1145/3290382

#### 1 INTRODUCTION

To support platform-independent concurrent programming, languages like C/C++11 and Java9 provide several types of memory accesses and high-level fence commands. Compilers of these languages are required to map the high-level primitives to instructions of mainstream architectures: in particular, x86-TSO [Owens et al. 2009], ARMv7 and POWER [Alglave et al. 2014], and ARMv8 [Pulte et al. 2018]. In this paper, we focus on proving the correctness of such mappings. Correctness amounts to showing that for every source program P, the set of behaviors allowed by the target architecture for the mapped program (P) (the program obtained by pointwise mapping the instructions in P) is contained in the set of behaviors allowed by the language-level model for P. Establishing such claim is a major part of a compiler correctness proof, and it is required for demonstrating the implementability of concurrency semantics. P

Accordingly, it has been an active research topic. In the case of C/C++11, Batty et al. [2011] established the correctness of a mapping to x86-TSO, while Batty et al. [2012] addressed the

Authors' addresses: Anton Podkopaev, St. Petersburg University, St. Petersburg, Russia, JetBrains Research, St. Petersburg, Russia, MPI-SWS, Germany, anton.podkopaev@jetbrains.com; Ori Lahav, Tel Aviv University, Israel, orilahav@tau.ac.il; Viktor Vafeiadis, MPI-SWS, Saarland Informatics Campus, Germany, viktor@mpi-sws.org.

Permission to make digital or hard copies of part or all of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for third-party components of this work must be honored. For all other uses, contact the owner/author(s).

© 2019 Copyright held by the owner/author(s).

2475-1421/2019/1-ART69

https://doi.org/10.1145/3290382

<sup>&</sup>lt;sup>1</sup>In the rest of this paper we refer to these mappings as "compilation", leaving compiler optimizations out of our scope.

mapping to POWER and ARMv7. However, the correctness claims of Batty et al. [2012] were subsequently found to be incorrect [Lahav et al. 2017; Manerkar et al. 2016], as they mishandled the combination of sequentially consistent accesses with weaker accesses. Lahav et al. [2017] developed RC11, a repaired version of C/C++11, and established (by pen-and-paper proof) the correctness of the suggested compilation schemes to x86-TSO, POWER and ARMv7. Beyond (R)C11, however, there are a number of other proposed higher-level semantics, such as JMM [Manson et al. 2005], OCaml [Dolan et al. 2018], Promise [Kang et al. 2017], LLVM [Chakraborty and Vafeiadis 2017], Linux kernel memory model [Alglave et al. 2018], AE-justification [Jeffrey and Riely 2016], Bubbly [Pichon-Pharabod and Sewell 2016], and WeakestMO [Chakraborty and Vafeiadis 2019], for which only a handful of compilation correctness results have been developed.

As witnessed by a number of known incorrect claims and proofs, these correctness results may be very difficult to establish. The difficulty stems from the typical large gap between the high-level programming language concurrency features and semantics, and the architecture ones. In addition, since hardware models differ in their strength (*e.g.*, which dependencies are preserved) and the primitives they support (barriers and atomic accesses), each hardware model may require a new challenging proof.

To address this problem, we propose to modularize the compilation correctness proof to go via an intermediate model, which we call IMM (for Intermediate Memory Model). IMM contains features akin to a language-level model (such as relaxed and release/acquire accesses as well as compare-and-swap primitives), but gives them a hardware-style declarative (a.k.a. axiomatic) semantics referring to explicit syntactic dependencies. IMM is very useful for structuring the compilation proofs and for enabling proof reuse: for N language semantics and M architectures, using IMM, we can reduce the number of required results from  $N \times M$  to N + M, and moreover each of these N + M proofs is typically easier than a corresponding end-to-end proof because of a smaller semantic gap between IMM and another model than between a given language-level and hardware-level model. The formal definition of IMM contains a number of subtle points as it has to be weaker than existing hardware models, and yet strong enough to support compilation from language-level models. (We discuss these points in §3.)

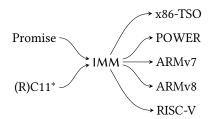

As summarized in Fig. 1, besides introducing IMM and proving that it is a sound abstraction over a range of hardware memory models, we prove the correctness of compilation from fragments of C11 and RC11 without non-atomic and SC accesses (denoted by (R)C11\*) and from the language-level memory model of the "promising semantics" of Kang et al. [2017] to IMM.

The latter proof is the most challenging. The promising semantics is a recent prominent attempt to solve the infamous "out-of-thin-air" problem in programming language concurrency semantics [Batty et al. 2015; Boehm and Dem-

Fig. 1. Results proved in this paper.

sky 2014] without sacrificing performance. To allow efficient implementation on modern hardware platforms, the promising semantics allows threads to execute instructions out of order by having them "promise" (i.e., pre-execute) future stores. To avoid out-of-thin-air values, every step in the promising semantics is subject to a *certification* condition. Roughly speaking, this means that thread i may take a step to a state  $\sigma$ , only if there exists a sequence of steps of thread i starting from  $\sigma$  to

<sup>&</sup>lt;sup>2</sup>Being defined on a per-execution basis, IMM is not suitable as language-level semantics (see [Batty et al. 2015]). Indeed, it disallows various compiler optimizations that remove syntactic dependencies.

a state  $\sigma'$  in which i indeed performed (fulfilled) all its pre-executed writes (promises). Thus, the validity of a certain trace in the promising semantics depends on existence of other traces.

In mapping the promising semantics to IMM, we therefore have the largest gap to bridge: a non-standard operational semantics on the one side versus a hardware-like declarative semantics on the other side. To relate the two semantics, we carefully construct a traversal strategy on IMM execution graphs, which gives us the order in which we can execute the promising semantics machine, keep satisfying its certification condition, and finally arrive at the same outcome.

The end-to-end result is the correctness of an efficient mapping from the promising semantics of Kang et al. [2017] to the main hardware architectures. While there are two prior compilation correctness results from promising semantics to POWER and ARMv8 [Kang et al. 2017; Podkopaev et al. 2017], neither result is adequate. The POWER result [Kang et al. 2017] considered a simplified (suboptimal) compilation scheme and, in fact, we found out that its proof is incorrect in its handling of SC fences (see §8 for more details). In addition, its proof strategy, which is based on program transformations account for weak behaviors [Lahav and Vafeiadis 2016], cannot be applied to ARM. The ARMv8 result [Podkopaev et al. 2017] handled only a small restricted subset of the concurrency features of the promising semantics and an operational hardware model (ARMv8-POP) that was later abandoned by ARM in favor of a rather different declarative model [Pulte et al. 2018].

By encompassing all features of the promising semantics, our proof uncovered a subtle correctness problem in the conjectured compilation scheme of its read-modify-write (RMW) operations to ARMv8 and to the closely related RISC-V model. We found out that exclusive load and store operations in ARMv8 and RISC-V are weaker than those of POWER and ARMv7, following their models by Alglave et al. [2014], so that the intended compilation of RMWs is broken (see Example 3.10). Thus, the mapping to ARMv8 that we proved correct places a weak barrier (specifically ARM's "Id fence") after every RMW.3 To keep IMM as a sound abstraction of ARMv8 and allow reuse of IMM in a future improvement of the promising semantics, we equip IMM with two types of RMWs: usual ones that are compiled to ARMv8 without the extra barrier, and stronger ones that require the extra barrier. To establish the correctness of the mapping from the (existing) promising semantics to IMM, we require that RMW instructions of the promising semantics are mapped to IMM's strong RMWs.

Finally, to ensure correctness of such subtle proofs, our results are all mechanized in Coq (~33K LOC). To the best of our knowledge, this constitutes the first mechanized correctness of compilation result from a high-level programming language concurrency model to a model weaker than x86-TSO. We believe that the existence of Coq proof scripts relating the different models may facilitate the development and investigation of weak memory models in the future, as well as the possible modifications of IMM to accommodate new and revised hardware and/or programming languages concurrency semantics.

The rest of this paper is organized as follows. In §2 we present IMM's program syntax and its mapping to execution graphs. In §3 we define IMM's consistency predicate. In §4 we present the mapping of IMM to main hardware and establish its correctness. In §5 we present the mappings from C11 and RC11 to IMM and establish their correctness. Sections 6 and 7 concern the mapping of the promising semantics of Kang et al. [2017] to IMM. To assist the reader, we discuss first (§6) a restricted fragment (with only relaxed accesses), and later (§7) extend our results and proof outline to the full promising model. Finally, we discuss related work in §8 and conclude in §9.

Supplementary material for this paper, including the Coq development, is publicly available at http://plv.mpi-sws.org/imm/.

<sup>&</sup>lt;sup>3</sup>Recall that RMWs are relatively rare. The performance cost of this fixed compilation scheme is beyond the scope of this paper, and so is the improvement of the promising semantics to recover the correctness of the barrier-free compilation.

```

Domains

Modes

n \in \mathbb{N}

Natural numbers

o_R ::= rlx \mid acq

Read modes

v \in Val \triangleq \mathbb{N}

Values

o_{\mathsf{W}} ::= \mathsf{rlx} \mid \mathsf{rel}

Write modes

x \in \mathsf{Loc} \triangleq \mathbb{N}

Locations

o_F ::= acq \mid rel \mid acqrel \mid sc

Fence modes

o_{RMW} ::= normal \mid strong

RMW modes

r \in \text{Reg}

Registers

i \in \mathsf{Tid}

Thread identifiers

Exp \ni e ::= r \mid n \mid e_1 + e_2 \mid e_1 - e_2 \mid ...

\begin{array}{l} \operatorname{Inst}\ni inst ::= r := e \ \mid \ \mathbf{if} \ e \ \mathbf{goto} \ n \ \mid \ [e]^{o_{\mathbb{N}}} := e \ \mid \ r := [e]^{o_{\mathbb{R}}} \ \mid \\ r := \operatorname{FADD}_{O_{\mathbb{R}\mathsf{M}\mathsf{M}}}^{O_{\mathbb{R}},o_{\mathbb{N}}}(e,e) \ \mid \ r := \operatorname{CAS}_{O_{\mathbb{R}\mathsf{M}\mathsf{M}}}^{O_{\mathbb{R}},o_{\mathbb{N}}}(e,e,e) \ \mid \ \mathbf{fence}^{o_{\mathbb{F}}} \end{array}

sprog \in SProg \triangleq \mathbb{N} \stackrel{fin}{\rightharpoonup} Inst Sequential programs

prog : Tid \rightarrow SProg

Programs

```

Fig. 2. Programming language syntax.

#### 2 PRELIMINARIES: FROM PROGRAMS TO EXECUTION GRAPHS

Following the standard declarative (a.k.a. axiomatic) approach of defining memory consistency models [Alglave et al. 2014], the semantics of IMM programs is given in terms of *execution graphs* which partially order *events*. This is done in two steps. First, the program is mapped to a large set of execution graphs in which the read values are completely arbitrary. Then, this set is filtered by a consistency predicate, and only IMM-*consistent* execution graphs determine the possible outcomes of the program under IMM. Next, we define IMM's programming language (§2.1), define IMM's execution graphs (§2.2), and present the construction of execution graphs from programs (§2.3). The next section (§3) is devoted to present IMM's consistency predicate.

Before we start we introduce some notation for relations and functions. Given a binary relation R, we write  $R^?$ ,  $R^+$ , and  $R^*$  respectively to denote its reflexive, transitive, and reflexive-transitive closures. The inverse relation is denoted by  $R^{-1}$ , and dom(R) and codom(R) denote R's domain and codomain. We denote by  $R_1$ ;  $R_2$  the left composition of two relations  $R_1$ ,  $R_2$ , and assume that; binds tighter than  $\cup$  and  $\setminus$ . We write  $R|_{\text{limm}}$  for the set of all  $immediate\ R\ edges$ :  $R|_{\text{limm}} \triangleq R \setminus R$ ; R. We denote by [A] the identity relation on a set A. In particular, [A]; R;  $[B] = R \cap (A \times B)$ . For finite sets  $\{a_1, \ldots, a_n\}$ , we omit the set parentheses and write  $[a_1, \ldots, a_n]$ . Finally, for a function  $f: A \to B$  and a set  $X \subseteq A$ , we write f[X] to denote the set  $\{f(x) \mid x \in X\}$ .

# 2.1 Programming Language

IMM is formulated over the language defined in Fig. 2 with C/C++11-like concurrency features. Expressions are constructed from registers (local variables) and integers, and represent values and locations. Instructions include assignments and conditional branching, as well as memory operations. Intuitively speaking, an assignment r := e assigns the value of e to register r (involving no memory access); **if** e **goto** n jumps to line n of the program iff the value of e is not 0; the write  $[e_1]^{o_N} := e_2$  stores the value of  $e_2$  in the address given by  $e_1$ ; the read  $r := [e]^{o_R}$  loads the value in address e to register e; e is an address e to register e; e in the address given by e in the read e in address e to register e; e in the value to e in address e to the value of e in the two values are the same, it replaces the value stored in e by the value of e, and fence instructions **fence** e are used to place global barriers.

The memory operations are annotated with *modes* that are ordered as follows:

```

\sqsubseteq \triangleq \{\langle \texttt{rlx}, \texttt{acq} \rangle, \langle \texttt{rlx}, \texttt{rel} \rangle, \langle \texttt{acq}, \texttt{acqrel} \rangle, \langle \texttt{rel}, \texttt{acqrel} \rangle, \langle \texttt{acqrel}, \texttt{sc} \rangle\}^*

```

Whenever  $o_1 \sqsubseteq o_2$ , we say that  $o_2$  is stronger than  $o_1$ : it provides more consistency guarantees but is more costly to implement. RMWs include two modes— $o_R$  for the read part and  $o_W$  for the write part—as well as a third (binary) mode o<sub>RMW</sub> used to denote certain RMWs as stronger ones.

In turn, sequential programs are finite maps from N to instructions, and (concurrent) programs are top-level parallel composition of sequential programs, defined as mappings from a finite set Tid of thread identifiers to sequential programs. In our examples, we write sequential programs as sequences of instructions delimited by ';' (or line breaks) and use '||' for parallel composition.

Remark 1. C/C++11 sequentially consistent (SC) accesses are not included in IMM. They can be simulated, nevertheless, using SC fences following the compilation scheme of C/C++11 (see [Lahav et al. 2017]). We note that SC accesses are also not supported by the promising semantics.

## 2.2 Execution Graphs

*Definition 2.1.* An *event*,  $e \in Event$ , takes one of the following forms:

- Non-initialization event:  $\langle i, n \rangle$  where  $i \in \text{Tid}$  is a thread identifier, and  $n \in \mathbb{Q}$  is a serial number inside each thread.

- Initialization event:  $\langle \text{init } x \rangle$  where  $x \in \text{Loc}$  is the location being initialized.

We denote by Init the set of all initialization events. The functions tid and sn return the (noninitialization) event's thread identifier and serial number.

Our representation of events induces a sequenced-before partial order on events given by:

```

e_1 < e_2 \Leftrightarrow (e_1 \in \mathsf{Init} \land e_2 \notin \mathsf{Init}) \lor (e_1 \notin \mathsf{Init} \land e_2 \notin \mathsf{Init} \land \mathsf{tid}(e_1) = \mathsf{tid}(e_2) \land \mathsf{sn}(e_1) < \mathsf{sn}(e_2))

```

Initialization events precede all non-initialization events, while events of the same thread are ordered according to their serial numbers. We use rational numbers as serial numbers to be able to easily add an event between any two events.

*Definition 2.2.* A *label*,  $l \in Lab$ , takes one of the following forms:

- Read label:  $R_s^{o_R}(x, v)$  where  $x \in Loc$ ,  $v \in Val$ ,  $o_R \in \{rlx, acq\}$ , and  $s \in \{not-ex, ex\}$ .

- Write label:  $W_{O_{RMW}}^{O_W}(x, v)$  where  $x \in Loc, v \in Val, o_W \in \{rlx, rel\}, and o_{RMW} \in \{normal, strong\}.$

- Fence label:  $F^{o_F}$  where  $o_F \in \{acq, rel, acqrel, sc\}$ .

Read labels include a location, a value, and a mode, as well as an "is exclusive" flag s. Exclusive reads stem from an RMW and are usually followed by a corresponding write. An exception is the case of a "failing" CAS (when the read value is not the expected one), where the exclusive read is not followed by a corresponding write. Write labels include a location, a value, and a mode, as well as a flag marking certain writes as strong. This will be used to differentiate the strong RMWs from the normal ones. Finally, a fence label includes just a mode.

Definition 2.3. An execution G consists of:

- (1) a finite set G.E of events. Using G.E and the partial order < on events, we derive the program order (a.k.a. sequenced-before) relation in  $G: G.po \triangleq [G.E]; <; [G.E].$  For  $i \in Tid$ , we denote by  $G.E_i$  the set  $\{a \in G.E \mid tid(a) = i\}$ , and by  $G.E_{\neq i}$  the set  $\{a \in G.E \mid tid(a) \neq i\}$ .

- (2) a labeling function  $G.1ab: G.E \rightarrow Lab$ . The labeling function naturally induces functions G.mod, G.loc, and G.val that return (when applicable) an event's label mode, location, and value. We use G.R, G.W, G.F to denote the subsets of G.E of events labeled with the respective type. We use obvious notations to further restrict the different modifiers of the event (e.g.,  $G.W(x) = \{w \in G.W \mid G.loc(w) = x\}$  and  $G.F^{\supseteq o} = \{f \in G.F \mid G.mod(f) \supseteq o\}$ ). We assume that  $G.lab(\langle init x \rangle) = W_{normal}^{rlx}(x, 0)$  for every  $\langle init x \rangle \in G.E.$

| When $sprog(pc) =$                      | we have the following constraints relating $pc, pc', \Phi, \Phi', G, G', \Psi, \Psi', S, S'$ :                                                                              |

|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| r := e                                  | $pc' = pc + 1 \land \Phi' = \Phi[r := \Phi(e)] \land G' = G \land \Psi' = \Psi[r := \Psi(e)] \land S' = S$                                                                  |

| if e goto n                             | $(\Phi(e) \neq 0 \Rightarrow pc' = n) \land (\Phi(e) = 0 \Rightarrow pc' = pc + 1) \land$                                                                                   |

|                                         | $G = G' \wedge \Phi = \Phi' \wedge \Psi' = \Psi \wedge S' = S \cup \Psi(e)$                                                                                                 |

| $[e_1]^{o_{W}} := e_2$                  | $G' = \operatorname{add}_{G}(i, W_{\operatorname{normal}}^{O_{W}}(\Phi(e_{1}), \Phi(e_{2})), \emptyset, \Psi(e_{2}), \Psi(e_{1}), S, \emptyset) \wedge$                     |

|                                         | $pc' = pc + 1 \land \Phi' = \Phi \land \Psi' = \Psi \land S' = S$                                                                                                           |

| $r:=[e]^{O_{\mathbb{R}}}$               | $\exists v. \ G' = \operatorname{add}_{G}(i, R^{o_{R}}_{not-ex}(\Phi(e), v), \emptyset, \emptyset, \Psi(e), S, \emptyset) \ \land$                                          |

|                                         | $pc' = pc + 1 \land \Phi' = \Phi[r := v] \land \Psi' = \Psi[r := \{\langle i, next_G \rangle\}] \land S' = S$                                                               |

| $r := FADD^{o_R,o_W}_{o_RMW}(e_1,e_2)$  | $\exists v. \ \mathbf{let} \ a_{R}, G_{R} = \langle i, next_G \rangle, add_G(i, R^{o_{R}}_{ex}(\Phi(e_1), v), \emptyset, \emptyset, \Psi(e_1), S, \emptyset) \ \mathbf{in}$ |

|                                         | $G' = add_{G_{R}}(i, W^{O_{N}}_{o_{RNW}}(\Phi(e_1), \upsilon + \Phi(e_2)), \{a_{R}\}, \{a_{R}\} \cup \Psi(e_2), \Psi(e_1), S, \emptyset) \land $                            |

|                                         | $pc' = pc + 1 \land \Phi' = \Phi[r := v] \land \Psi' = \Psi[r := \{a_{R}\}] \land S' = S$                                                                                   |

| $r := CAS^{o_R,o_W}_{o_RMW}(e,e_R,e_W)$ | $\exists v. \ \mathbf{let} \ a_{R}, G_{R} = \langle i, next_G \rangle, add_G(i, R^{O_{R}}_{ex}(\Phi(e), v), \emptyset, \emptyset, \Psi(e), S, \Psi(e_{R})) \ \mathbf{in}$   |

|                                         | $pc' = pc + 1 \land \Phi' = \Phi[r := v] \land \Psi' = \Psi[r := \{a_{R}\}] \land S' = S \land$                                                                             |

|                                         | $(v \neq \Phi(e_{R}) \Rightarrow G' = G_{R}) \land$                                                                                                                         |

|                                         | $(v = \Phi(e_{R}) \Rightarrow G' = add_{G_{R}}(i, W^{O_{M}}_{\mathcal{O}_{RMW}}(\Phi(e), \Phi(e_{W})), \{a_{R}\}, \Psi(e_{W}), \Psi(e), S, \emptyset))$                     |

| fence <sup>o</sup> F                    | $G' = \operatorname{add}_{G}(i, F^{o_{F}}, \emptyset, \emptyset, \emptyset, S, \emptyset) \land pc' = pc + 1 \land \Phi' = \Phi \land \Psi' = \Psi \land S' = S$            |

Fig. 3. The relation  $\langle sprog, pc, \Phi, G, \Psi, S \rangle \rightarrow_i \langle sprog, pc', \Phi', G', \Psi', S' \rangle$  representing a step of thread i.

- (3) a relation  $G.rmw \subseteq \bigcup_{x \in Loc} [G.R_{ex}(x)]; G.po|_{imm}; [G.W(x)], called RMW pairs. We require that <math>G.W_{strong} \subseteq codom(G.rmw).$

- (4) a relation  $G.data \subseteq [G.R]$ ; G.po; [G.W], called data dependency.

- (5) a relation G.addr  $\subseteq$  [G.R]; G.po; [G.R  $\cup$  G.W], called address dependency.

- (6) a relation  $G.ctrl \subseteq [G.R]$ ; G.po, called *control dependency*, that is forwards-closed under the program order: G.ctrl;  $G.po \subseteq G.ctrl$ .

- (7) a relation G.casdep  $\subseteq [G.R]$ ; G.po;  $[G.R_{ex}]$ , called CAS dependency.

- (8) a relation  $G.rf \subseteq \bigcup_{x \in Loc} G.W(x) \times G.R(x)$ , called *reads-from*, and satisfying: G.val(w) = G.val(r) for every  $\langle w, r \rangle \in G.rf$ ; and  $w_1 = w_2$  whenever  $\langle w_1, r \rangle, \langle w_2, r \rangle \in G.rf$  (that is,  $G.rf^{-1}$  is functional).

- (9) a strict partial order  $G.co \subseteq \bigcup_{x \in Loc} G.W(x) \times G.W(x)$ , called *coherence order* (a.k.a. *modification order*).

# 2.3 Mapping Programs to Executions

Sequential programs are mapped to execution graphs by means of an operational semantics. Its states have the form  $\sigma = \langle sprog, pc, \Phi, G, \Psi, S \rangle$ , where sprog is the thread's sequential program;  $pc \in \mathbb{N}$  points to the next instruction in sprog to be executed;  $\Phi : \text{Reg} \to \text{Val}$  maps register names to the values they store (extended to expressions in the obvious way); G is an execution graph (denoted by  $\sigma.G$ );  $\Psi : \text{Reg} \to \mathcal{P}(G.R)$  maps each register name to the set of events that were used to compute the register's value; and  $S \subseteq G.R$  maintains the set of events having a control dependency to the current program point. The  $\Psi$  and S components are used to calculate the dependency edges in  $G.\Psi$  is extended to expressions in the obvious way  $(e.g., \Psi(n) \triangleq \emptyset$  and  $\Psi(e_1 + e_2) \triangleq \Psi(e_1) \cup \Psi(e_2)$ ). Note that the executions graphs produced by this semantics represent traces of one thread, and as such, they are quite degenerate: G.po totally orders G.E and  $G.rf = G.co = \emptyset$ .

The *initial state* is  $\sigma_0(sprog) \triangleq \langle sprog, 0, \lambda r. 0, G_\emptyset, \lambda r. \emptyset, \emptyset \rangle$  ( $G_\emptyset$  denotes the empty execution), *terminal* states are those in which  $pc \notin dom(sprog)$ , and the transition relation is given in Fig. 3. It uses the notations next<sub>G</sub> to obtain the next serial number in a thread execution graph G (next<sub>G</sub>  $\triangleq$  |G.E|) and add<sub>G</sub> to append an event with thread identifier i and label l to G:

Definition 2.4. For an execution graph  $G, i \in \mathsf{Tid}, l \in \mathsf{Lab},$ and  $E_{\mathsf{rmw}}, E_{\mathsf{data}}, E_{\mathsf{addr}}, E_{\mathsf{ctrl}}, E_{\mathsf{casdep}} \subseteq$ G.R,  $add_G(i, l, E_{rmw}, E_{data}, E_{addr}, E_{ctrl}, E_{casdep})$  denotes the execution graph G' given by:

```

G'.E = G.E \uplus \{\langle i, next_G \rangle\}

G'.1ab = G.1ab \uplus \{\langle i, next_G \rangle \mapsto l\}

G'.data = G.data \uplus (E_{data} \times \{\langle i, next_G \rangle \})

G'.\mathsf{rmw} = G.\mathsf{rmw} \uplus (E_{\mathsf{rmw}} \times \{\langle i, \mathsf{next}_G \rangle\})

G'.addr = G.addr \uplus (E_{addr} \times \{\langle i, next_G \rangle \})

G'.\mathsf{ctrl} = G.\mathsf{ctrl} \uplus (E_{\mathsf{ctrl}} \times \{\langle i, \mathsf{next}_G \rangle\})

G'.co = G.co

G'.casdep = G.casdep \uplus (E_{casdep} \times \{\langle i, next_G \rangle \})

G'.rf = G.rf

```

Besides the explicit calculation of dependencies, the operational semantics is standard.

Example 2.5. The only novel ingredient is the CAS dependency relation, which tracks reads that affect the success of a CAS instruction. As an example, consider the following program.

The CAS instruction may produce a write event or not, depending on the value read from y and the value of register a, which is assigned at the read instruction from x. The case edge reflects the latter dependency in both representative execution graphs. The mapping of IMM's CAS instructions to POWER and ARM ensures that the casdep on the source execution graph

$$\begin{aligned} a &:= [x]^{\text{rlx}} \\ b &:= \text{CAS}_{\text{normal}}^{\text{rlx}, \text{rlx}}(y, a, 1) \\ [z]^{\text{rlx}} &:= 2 \end{aligned} \qquad \begin{aligned} & \mathsf{R}_{\text{not-ex}}^{\text{rlx}}(x, 0) \\ & \mathsf{R}_{\text{ex}}^{\text{rlx}}(y, 0) \end{aligned}$$

implies a control dependency to all po-later events in the target graph (see §4).

Next, we define program executions.

Definition 2.6. For an execution graph G and  $i \in Tid$ ,  $G|_i$  denotes the execution graph given by:

```

G|_{i}.E = G.E_{i}

G|_i.lab = G.lab|_{G,E_i}

G|_i.rmw = [G.E_i]; G.rmw; [G.E_i]

G|_i.data = [G.E_i]; G.data; [G.E_i]

G_i.addr = [G.E_i]; G.addr; [G.E_i]

G|_{i}.ctrl = [G.E_{i}]; G.ctrl; [G.E_{i}]

G|_i.casdep = [G.E_i]; G.casdep; [G.E_i]

G|_{i}.rf = G|_{i}.co = \emptyset

```

Definition 2.7 (Program executions). An execution graph G is a (full) execution graph of a program prog if for every  $i \in Tid$ , there exists a (terminal) state  $\sigma$  such that  $\sigma.G = G|_i$  and  $\sigma_0(prog(i)) \to_i^* \sigma$ .

Now, given the IMM-consistency predicate presented in the next section, we define the set of allowed outcomes.

*Definition 2.8. G* is *initialized* if  $\langle \text{init } x \rangle \in G.E$  for every  $x \in G.loc[G.E]$ .

*Definition 2.9.* A function  $O : Loc \rightarrow Val$  is:

- an outcome of an execution graph G if for every  $x \in Loc$ , either O(x) = G.val(w) for some G.co-maximal event  $w \in G.W(x)$ , or O(x) = 0 and  $G.W(x) = \emptyset$ .

- an outcome of a program prog under IMM if O is an outcome of some IMM-consistent initialized full execution graph of prog.

# 3 IMM: THE INTERMEDIATE MODEL

In this section, we introduce the consistency predicate of IMM. The first (standard) conditions require that every read reads from some write (codom(G.rf) = G.R), and that the coherence order totally orders the writes to each location (G.co totally orders G.W(x) for every  $x \in Loc$ ). In addition, we require (1) coherence, (2) atomicity of RMWs, and (3) global ordering, which are formulated in the rest of this section, with the help of several derived relations on events.

The rest of this section is described in the context of a given execution graph G, and the 'G.' prefix is omitted. In addition, we employ the following notational conventions: for every relation  $x \subseteq E \times E$ , we denote by  $x \in E \times E$ , we denote by  $x \in E \times E$ , we denote by  $x \in E \times E$ , we denote by  $x \in E \times E$ , we denote by  $x \in E \times E$ , we denote by  $x \in E \times E$ , we denote by  $x \in E \times E$ , we denote by  $x \in E \times E$ , we denote by  $x \in E \times E$ , we denote by  $x \in E \times E$ , we denote by  $x \in E \times E$ , we denote by  $x \in E \times E$ , we denote by  $x \in E \times E$ , we denote by  $x \in E \times E$ , we denote by  $x \in E \times E$ , we denote by  $x \in E \times E$ , we denote by  $x \in E \times E$ , we denote by  $x \in E \times E$ , we denote by  $x \in E \times E$ , we denote by  $x \in E \times E$ , we denote by  $x \in E \times E$ , we denote by  $x \in E \times E$ , we denote by  $x \in E \times E$ , we denote by  $x \in E \times E$ , we denote by  $x \in E \times E$ , we denote by  $x \in E \times E$ , we denote by  $x \in E \times E$ , we denote by  $x \in E \times E$ , we denote by  $x \in E \times E$ , we denote by  $x \in E \times E$ , we denote by  $x \in E \times E$ , we denote by  $x \in E \times E$ , where  $x \in E \times E$  is a function of  $x \in E \times E$ .

#### 3.1 Coherence

Coherence is a basic property of memory models that implies that programs with only one shared location behave as if they were running under sequential consistency. Hardware memory models typically enforce coherence by requiring that  $po|_{loc} \cup rf \cup co \cup rf^{-1}$ ; co is acyclic (a.k.a. SC-perlocation). Language models, however, strengthen the coherence requirement by replacing po with a "happens before" relation hb that includes po as well as inter-thread synchronization. Since IMM's purpose is to verify the implementability of language-level models, we take its coherence axiom to be close to those of language-level models. Following [Lahav et al. 2017], we therefore define the following relations:

```

\begin{split} \text{rs} &\triangleq [\texttt{W}] \, ; \, \mathsf{po}|_{\mathsf{loc}} \, ; \, [\texttt{W}] \cup [\texttt{W}] \, ; \, (\mathsf{po}|_{\mathsf{loc}}^? \, ; \, \mathsf{rf} \, ; \, \mathsf{rmw})^* & \textit{(release sequence)} \\ \text{release} &\triangleq ([\texttt{W}^{\mathsf{rel}}] \cup [\mathsf{F}^{\exists \mathsf{rel}}] \, ; \, \mathsf{po}) \, ; \, \mathsf{rs} & \textit{(release prefix)} \\ \text{sw} &\triangleq \mathsf{release} \, ; \, (\mathsf{rfi} \cup \mathsf{po}|_{\mathsf{loc}}^? \, ; \, \mathsf{rfe}) \, ; \, ([\mathsf{R}^{\mathsf{acq}}] \cup \mathsf{po} \, ; \, [\mathsf{F}^{\exists \mathsf{acq}}]) & \textit{(synchronizes with)} \\ \text{hb} &\triangleq (\mathsf{po} \cup \mathsf{sw})^+ & \textit{(happens-before)} \\ \text{fr} &\triangleq \mathsf{rf}^{-1} \, ; \, \mathsf{co} & \textit{(from-read/read-before)} \\ \text{eco} &\triangleq \mathsf{rf} \cup \mathsf{co} \, ; \, \mathsf{rf}^? \cup \mathsf{fr} \, ; \, \mathsf{rf}^? & \textit{(extended coherence order)} \end{split}

```

We say that G is coherent if hb; eco? is irreflexive, or equivalently  $\mathsf{hb}|_{\mathsf{loc}} \cup \mathsf{rf} \cup \mathsf{co} \cup \mathsf{fr}$  is acyclic.

Example 3.1 (Message passing). Coherence disallows the weak behavior of the MP litmus test:

To the right, we present the execution yielding the annotated weak outcome. The rf-edges and the induced fr-edge are determined by the annotated outcome. The displayed execution is inconsistent because the rf-edge between the release write and the acquire read constitutes an sw-edge, and hence there is an hb; fr cycle.

*Remark 2.* Adept readers may notice that our definition of sw is stronger (namely, our sw is larger) than the one of RC11 [Lahav et al. 2017], which (following the fixes of Vafeiadis et al. [2015] to C/C++11's original definition) employs the following definitions:

$$\begin{split} & rs_{RC11} \triangleq [\textbf{W}]; po|_{loc}^?; (\textbf{rf}; \textbf{rmw})^* & release_{RC11} \triangleq ([\textbf{W}^{rel}] \cup [\textbf{F}^{\exists rel}]; po); \textbf{rs}_{RC11} \\ & sw_{RC11} \triangleq release; \textbf{rf}; ([\textbf{R}^{acq}] \cup po; [\textbf{F}^{\exists acq}]) & hb_{RC11} \triangleq (po \cup sw_{RC11})^+ \end{split}$$

The reason for this discrepancy is our aim to allow the splitting of release writes and RMWs into release fences followed by relaxed operations. Indeed, as explained in §4.1, the soundness

<sup>&</sup>lt;sup>4</sup> We use program comments notation to refer to the read values in the behavior we discuss. These can be formally expressed as program outcomes (Def. 2.9) by storing the read values in distinguished memory locations. In addition, for conciseness, we do not show the implicit initialization events and the rf and co edges from them, and include the  $o_{RMW}$  subscript only for writes in codom(G.rmw) (recall that  $G.W_{strong} \subseteq codom(G.rmw)$ ).

of this transformation allows us to simplify our proofs. In RC11 [Lahav et al. 2017], as well as in C/C++11 [Batty et al. 2011], this rather intuitive transformation, as we found out, is actually unsound. To see this consider the following example:

$$\begin{aligned} [y]^{\text{rlx}} &:= 1 \\ [x]^{\text{rel}} &:= 1 \end{aligned} \middle\| a &:= \text{FADD}^{\text{acq,rel}}(x,1) \; \text{$/\!\!/ 1$} \\ |b| &:= [x]^{\text{acq}} \; \text{$/\!\!/ 3$} \\ |c| &:= [y]^{\text{rlx}} \; \text{$/\!\!/ 0$} \end{aligned}$$

(R)C11 disallows the annotated behavior, due in particular to the release sequence formed from the release exclusive write to x in the second thread to its subsequent relaxed write. However, if we split the increment to **fence**<sup>rel</sup>;  $a := \mathsf{FADD}^{\mathsf{acq}, rlx}(x, 1)$  (which intuitively may seem stronger), the release sequence will no longer exist, and the annotated behavior will be allowed. IMM overcomes this problem by strengthening sw in a way that ensures a synchronization edge for the transformed program as well. In §4.1, we establish the soundness of this splitting transformation in general. In addition, note that, as we show in §4, existing hardware support IMM's stronger synchronization without strengthening the intended compilation schemes. On the other hand, in our proof concerning the promising semantics in §7, it is more convenient to use RC11's definition of sw, which results in a (provably) stronger (namely, allowing less behaviors) model that still accounts for all the behaviors of the promising semantics.<sup>5</sup>

# 3.2 RMW Atomicity

Atomicity of RMWs simply states that the load of a successful RMW reads from the immediate co-preceding write before the RMW's store. Formally, rmw  $\cap$  (fre; coe) =  $\emptyset$ , which says that there is no other write ordered between the load and the store of an RMW.

Example 3.2 (Violation of RMW atomicity). The following behavior violates the fetch-and-add atomicity and is disallowed by all known weak memory models.

$$a := \operatorname{FADD}^{\operatorname{rlx},\operatorname{rlx}}_{\operatorname{normal}}(x,1) \ /\!\!/ 0 \ \bigg\| \begin{bmatrix} x \end{bmatrix}^{\operatorname{rlx}} := 2 \\ b := \begin{bmatrix} x \end{bmatrix}^{\operatorname{rlx}} \ /\!\!/ 1 \ \bigg\| \begin{cases} \operatorname{Rex}^{\operatorname{rlx}}(x,0) & \text{fre} \\ \operatorname{Rex}^{\operatorname{rlx}}(x,0) & \text{coe} & \text{or} \\ \operatorname{Wrlx}_{\operatorname{normal}}(x,1) & \text{fre} \\ \operatorname{Rex}^{\operatorname{rlx}}(x,2) & \text{or} \\ \operatorname{Rex}^{\operatorname{rlx}}(x,2)$$

To the right, we present an inconsistent execution corresponding to the outcome omitting the initialization event for conciseness. The rf edges and the induced fre edge are forced by the annotated outcome, while the coe edge is forced because of coherence: i.e., ordering the writes in the reverse order yields a coherence violation. The atomicity violation is thus evident.

#### 3.3 **Global Ordering Constraint**

The third condition—the global ordering constraint—is the most complicated and is used to rule out out-of-thin-air behaviors. We will incrementally define a relation ar that we require to be acyclic.

First of all, ar includes the external reads-from relation, rfe, and the ordering guarantees induced by memory fences and release/acquire accesses. Specifically, release writes enforce an ordering to any previous event of the same thread, acquire reads enforce the ordering to subsequent events of the same thread, while fences are ordered with respect to both prior and subsequent events. As a final condition, release writes are ordered before any subsequent writes to the same location: this is needed for maintaining release sequences.

$$bob \triangleq po; [W^{rel}] \cup [R^{acq}]; po \cup po; [F] \cup [F]; po \cup [W^{rel}]; po|_{loc}; [W] \qquad (\textit{barrier order})$$

<sup>&</sup>lt;sup>5</sup>The C++ committee is currently revising the release sequence definition aiming to simplify it and relate it to its actual uses. The analysis here may provide further input to that discussion.

$$ar \triangleq rfe \cup bob \cup ...$$

(acyclicity relation, more cases to be added)

Release/acquire accesses and fences in IMM play a double role: they induce synchronization similar to RC11 as discussed in §3.1 and also enforce intra-thread instruction ordering as in hardware models. The latter role ensures the absence of 'load buffering' behaviors in the following examples.

*Example 3.3 (Load buffering with release writes).* Consider the following program, whose annotated outcome disallowed by ARM, POWER, and the promising semantics.<sup>6</sup>

$$\begin{aligned} a &:= [x]^{\text{rlx}} \; /\!\!/ 1 \\ [y]^{\text{rel}} &:= 1 \end{aligned} \begin{vmatrix} b &:= [y]^{\text{rlx}} \; /\!\!/ 1 \\ [x]^{\text{rel}} &:= 1 \end{vmatrix} = 1 \end{aligned} \begin{vmatrix} \mathsf{R}^{\text{rlx}}_{\text{not-ex}}(x,1) & \mathsf{R}^{\text{rlx}}_{\text{not-ex}}(y,1) \\ \downarrow \text{bob} \\ \mathsf{W}^{\text{rel}}(y,1) & \mathsf{rfe} \end{vmatrix} + \mathsf{R}^{\text{rlx}}_{\text{not-ex}}(y,1) \\ \downarrow \text{bob} \\ \mathsf{W}^{\text{rel}}(x,1) & \mathsf{R}^{\text{rlx}}_{\text{not-ex}}(y,1) \end{vmatrix}$$

IMM disallows the outcome because of the bob  $\cup$  rfe cycle.

*Example 3.4 (Load buffering with acquire reads).* Consider a variant of the previous program with acquire loads and relaxed stores:

IMM again declares the presented execution as inconsistent following both ARM and POWER, which forbid the annotated outcome. The promising semantics, in contrast, allows this outcome to support a higher-level optimization (namely, elimination of redundant acquire reads).

Besides orderings due to fences, hardware preserves certain orderings due to syntactic code dependencies. Specifically, whenever a write depends on some earlier read by a chain of syntactic dependencies or internal reads-from edges (which are essentially dependencies through memory), then the hardware cannot execute the write until it has finished executing the read, and so the ordering between them is preserved. We call such preserved dependency sequences the *preserved program order* (ppo) and include it in ar. In contrast, dependencies between read events are not always preserved, and so we do not incorporate them in the ar relation.

$$\begin{split} \mathsf{deps} &\triangleq \mathsf{data} \cup \mathsf{ctrl} \cup \mathsf{addr} \, ; \mathsf{po}^? \cup \mathsf{casdep} \cup [\mathsf{R}_{\mathsf{ex}}] \, ; \mathsf{po} \\ \mathsf{ppo} &\triangleq [\mathsf{R}] \, ; (\mathsf{deps} \cup \mathsf{rfi})^+ \, ; [\mathsf{W}] \\ \mathsf{ar} &\triangleq \mathsf{rfe} \cup \mathsf{bob} \cup \mathsf{ppo} \cup \ldots \end{split} \tag{$\mathit{syntactic dependencies}$}$$

The extended constraint rules out the weak behaviors of variants of the load buffering example that use syntactic dependencies to enforce an ordering.

*Example 3.5 (Load buffering with an address dependency).* Consider a variant of the previous program with an address-dependent read instruction in the middle of the first thread:

The displayed execution is IMM-inconsistent because of the addr; po;rfe; bob;rfe cycle. Hardware implementations cannot produce the annotated behavior because the write to y cannot be issued

<sup>&</sup>lt;sup>6</sup>In this and other examples, when saying whether a behavior of a program is allowed by ARM/POWER, we implicitly mean the intended mapping of the program's primitive accesses to ARM/POWER. See §4 for details.

Bridging the Gap between Programming Languages and Hardware Weak Memory Models 69:11

until it has been determined that its address does not alias with y + a, which cannot be determined until the value of x has been read.

Similar to syntactic dependencies, rfi edges are guaranteed to be preserved only on dependency paths from a read to a write, not otherwise.

*Example 3.6 (rfi is not always preserved).* Consider the following program, whose annotated outcome is allowed by ARMv8.

To the right, we show the corresponding execution (the rf edges are forced because of the outcome). Had we included rfi unconditionally as part of ar, we would have disallowed the behavior, because it would have introduced an ar edge between events  $e_1$  and  $e_2$ , and therefore an ar cycle.

Note that we do not include fri in ppo since it is not preserved in ARMv7 [Alglave et al. 2014] (unlike in x86-TSO, POWER, and ARMv8). Thus, as ARMv7 (as well as the Flowing and POP models of ARM in [Flur et al. 2016]), IMM allows the weak behavior from [Lahav and Vafeiadis 2016, Âğ6].

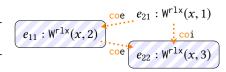

Next, we include  $detour \triangleq (coe; rfe) \cap po$  in ar. It captures the case when a read r does not read from an earlier write w to the same location but from a write w' of a different thread. In this case, both ARM and POWER enforce an ordering between w and r. Since the promising semantics also enforces such orderings (due to the certification requirement in every future memory, see §7), IMM also enforces the ordering by including detour in ar.

*Example 3.7 (Enforcing detour).* The annotated behavior of the following program is disallowed by POWER, ARM, and the promising semantics, and so it must be disallowed by IMM.

$$[x]^{\text{rlx}} := 1 \left\| \begin{array}{c} a := [z]^{\text{rlx}} \ \, /\! \, 1 \\ [x]^{\text{rlx}} := a - 1 \\ b := [x]^{\text{rlx}} \ \, /\! \, 1 \\ [y]^{\text{rlx}} := b \end{array} \right\| c := [y]^{\text{rlx}} \ \, /\! \, 1 \\ c := [y]^{\text{rlx}} \ \, /\! \, 1 \\ c := [y]^{\text{rlx}} \ \, /\! \, 1 \\ c := [y]^{\text{rlx}} \ \, /\! \, 1 \\ c := [y]^{\text{rlx}} \ \, /\! \, 1 \\ c := [y]^{\text{rlx}} \ \, /\! \, 1 \\ c := [y]^{\text{rlx}} \ \, /\! \, 1 \\ c := [y]^{\text{rlx}} \ \, /\! \, 1 \\ c := [y]^{\text{rlx}} \ \, /\! \, 1 \\ c := [y]^{\text{rlx}} \ \, /\! \, 1 \\ c := [y]^{\text{rlx}} \ \, /\! \, 1 \\ c := [y]^{\text{rlx}} \ \, /\! \, 1 \\ c := [y]^{\text{rlx}} \ \, /\! \, 1 \\ c := [y]^{\text{rlx}} \ \, /\! \, 1 \\ c := [y]^{\text{rlx}} \ \, /\! \, 1 \\ c := [y]^{\text{rlx}} \ \, /\! \, 1 \\ c := [y]^{\text{rlx}} \ \, /\! \, 1 \\ c := [y]^{\text{rlx}} \ \, /\! \, 1 \\ c := [y]^{\text{rlx}} \ \, /\! \, 1 \\ c := [y]^{\text{rlx}} \ \, /\! \, 1 \\ c := [y]^{\text{rlx}} \ \, /\! \, 1 \\ c := [y]^{\text{rlx}} \ \, /\! \, 1 \\ c := [y]^{\text{rlx}} \ \, /\! \, 1 \\ c := [y]^{\text{rlx}} \ \, /\! \, 1 \\ c := [y]^{\text{rlx}} \ \, /\! \, 1 \\ c := [y]^{\text{rlx}} \ \, /\! \, 1 \\ c := [y]^{\text{rlx}} \ \, /\! \, 1 \\ c := [y]^{\text{rlx}} \ \, /\! \, 1 \\ c := [y]^{\text{rlx}} \ \, /\! \, 1 \\ c := [y]^{\text{rlx}} \ \, /\! \, 1 \\ c := [y]^{\text{rlx}} \ \, /\! \, 1 \\ c := [y]^{\text{rlx}} \ \, /\! \, 1 \\ c := [y]^{\text{rlx}} \ \, /\! \, 1 \\ c := [y]^{\text{rlx}} \ \, /\! \, 1 \\ c := [y]^{\text{rlx}} \ \, /\! \, 1 \\ c := [y]^{\text{rlx}} \ \, /\! \, 1 \\ c := [y]^{\text{rlx}} \ \, /\! \, 1 \\ c := [y]^{\text{rlx}} \ \, /\! \, 1 \\ c := [y]^{\text{rlx}} \ \, /\! \, 1 \\ c := [y]^{\text{rlx}} \ \, /\! \, 1 \\ c := [y]^{\text{rlx}} \ \, /\! \, 1 \\ c := [y]^{\text{rlx}} \ \, /\! \, 1 \\ c := [y]^{\text{rlx}} \ \, /\! \, 1 \\ c := [y]^{\text{rlx}} \ \, /\! \, 1 \\ c := [y]^{\text{rlx}} \ \, /\! \, 1 \\ c := [y]^{\text{rlx}} \ \, /\! \, 1 \\ c := [y]^{\text{rlx}} \ \, /\! \, 1 \\ c := [y]^{\text{rlx}} \ \, /\! \, 1 \\ c := [y]^{\text{rlx}} \ \, /\! \, 1 \\ c := [y]^{\text{rlx}} \ \, /\! \, 1 \\ c := [y]^{\text{rlx}} \ \, /\! \, 1 \\ c := [y]^{\text{rlx}} \ \, /\! \, 1 \\ c := [y]^{\text{rlx}} \ \, /\! \, 1 \\ c := [y]^{\text{rlx}} \ \, /\! \, 1 \\ c := [y]^{\text{rlx}} \ \, /\! \, 1 \\ c := [y]^{\text{rlx}} \ \, /\! \, 1 \\ c := [y]^{\text{rlx}} \ \, /\! \, 1 \\ c := [y]^{\text{rlx}} \ \, /\! \, 1 \\ c := [y]^{\text{rlx}} \ \, /\! \, 1 \\ c := [y]^{\text{rlx}}$$

If we were to exclude detour from the acyclicity condition, the execution of the program shown above to the right would have been allowed by IMM.

We move on to a constraint about SC fences. Besides constraining the ordering of events from the same thread, SC fences induce inter-thread orderings whenever there is a coherence path between them. Following the RC11 model [Lahav et al. 2017], we call this relation psc and include it in ar.

$$psc \triangleq [F^{sc}]; hb; eco; hb; [F^{sc}]$$

(partial SC fence order)

$ar \triangleq rfe \cup bob \cup ppo \cup detour \cup psc \cup ...$

Example 3.8 (Independent reads of independent writes). Similar to POWER, IMM is not "multi-copy atomic" [Maranget et al. 2012] (or "memory atomic" [Zhang et al. 2018]). In particular, it allows

the weak behavior of the IRIW litmus test even with release-acquire accesses. To forbid the weak behavior, one has to use SC fences:

The execution corresponding to the weak outcome is shown to the right. For soundness w.r.t. the promising semantics, IMM declares this execution to be inconsistent (which is also natural since it has an SC fence between every two instructions). It does so due to the psc cycle: each fence reaches the other by a po; fr; rf; po  $\subseteq$  psc path. When the SC fences are omitted, since POWER allows the weak outcome, IMM allows it as well.

Example 3.9. To illustrate why we make psc part of ar, rather than a separate acyclicity condition (as in RC11), consider the following program, whose annotated outcome is forbidden by the promising semantics.

The execution corresponding to that outcome is shown to the right. For soundness w.r.t. the promising semantics, IMM declares this execution inconsistent, due to the ar cycle.  $\Box$

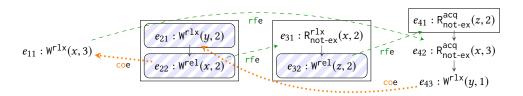

The final case we add to ar is to support the questionable semantics of RMWs in the promising semantics. The promising semantics requires the ordering between the store of a release RMW and subsequent stores to be preserved, something that is not generally guaranteed by ARMv8. For this reason, to be able to compile the promising semantics to IMM, and still keep IMM as a sound abstraction of ARMv8, we include the additional "RMW mode" in RMW instructions, which propagates to their induced write events. Then, we include  $[W_{strong}]$ ; po; [W] in ar, yielding the following (final) definition:

$$\texttt{ar} \triangleq \texttt{rfe} \cup \texttt{bob} \cup \texttt{ppo} \cup \texttt{detour} \cup \texttt{psc} \cup [\texttt{W}_{\texttt{strong}}] \, ; \texttt{po} \, ; [\texttt{W}]$$

*Example 3.10.* The following example demonstrates the problem in the intended mapping of the promising semantics to ARMv8.

The promising semantics disallows the annotated behavior (it requires a promise of y = 1, but this promise cannot be certified for a future memory that will not allow the atomic increment from 0—see §7.1 and Example 7.6). It is disallowed by IMM due to the ar cycle (from the read of y):

Bridging the Gap between Programming Languages and Hardware Weak Memory Models 69:13

Fig. 4. Compilation scheme from IMM to POWER.

ppo ; rfe ; bob ;  $[W_{strong}]$  ; po ; [W] ; rfe. Without additional barriers, ARMv8 allows this behavior. Thus, our mapping of IMM to ARMv8 places a barrier ("ld fence") after strong RMWs (see §4.2).  $\Box$

# 3.4 Consistency

Putting everything together, IMM-consistency is defined as follows.

*Definition 3.11. G* is called IMM-consistent if the following hold:

```

• codom(G.rf) = G.R. (rf-completeness)

• For every location x \in Loc, G.co totally orders G.W(x). (co-totality)

• G.hb; G.eco? is irreflexive. (coherence)

• G.rmw \cap (G.fre; G.coe) = \emptyset. (ATOMICITY)

• G.ar is acyclic. (NO-THIN-AIR)

```

#### 4 FROM IMM TO HARDWARE MODELS

In this section, we provide mappings from IMM to the main hardware architectures and establish their soundness. That is, if some behavior is allowed by a target architecture on a target program, then it is also allowed by IMM on the source of that program. Since the models of hardware we consider are declarative, we formulate the soundness results on the level of execution graphs, keeping the connection to programs only implicit. Indeed, a mapping of IMM instructions to real architecture instructions naturally induces a mapping of IMM execution graphs to target architecture execution graphs. Then, it suffices to establish that the consistency of a target execution graph (as defined by the target memory model) entails the IMM-consistency of its source execution graph. This is a common approach for studying declarative models, (see, e.g., [Vafeiadis et al. 2015]), and allows us to avoid orthogonal details of the target architectures' instruction sets.

Next, we study the mapping to POWER (§4.1) and ARMv8 (§4.2). We note that IMM can be straightforwardly shown to be weaker than x86-TSO, and thus the identity mapping (up to different syntax) is a correct compilation scheme from IMM to x86-TSO. The mapping to ARMv7 is closely related to POWER, and it is discussed in §4.1 as well. RISC-V [RISC-V 2018; RISCV in herd 2018] is stronger than ARMv8 and therefore soundness of mapping to it from IMM follows from the corresponding ARMv8 result.

# 4.1 From IMM to POWER

The intended mapping of IMM to POWER is presented schematically in Fig. 4. It follows the C/C++11 mapping [Mapping 2016] (see also [Maranget et al. 2012]): relaxed reads and writes are compiled down to plain machine loads and stores; acquire reads are mapped to plain loads followed by a control dependent instruction fence; release writes are mapped to plain writes preceded by a lightweight fence; acquire/release/acquire-release fences are mapped to POWER's lightweight fences; and SC fences are mapped to full fences. The compilation of RMWs requires a loop which repeatedly uses POWER's load-reserve/store-conditional instructions until the store-conditional

succeeds. RMWs are accompanied with barriers for acquire/release modes as reads and writes. CAS instructions proceed to the conditional write only after checking that the loaded value meets the required condition. Note that IMM's strong RMWs are compiled to POWER as normal RMWs.

To simplify our correctness proof, we take advantage of the fact that release writes and release RMWs are compiled down as their relaxed counterparts with a preceding **fence**<sup>rel</sup>. Thus, we consider the compilation as if it happens in two steps: first, release writes and RMWs are split to release fences and their relaxed counterparts; and then, the mapping of Fig. 4 is applied (for a program without release writes and release RMWs). Accordingly, we establish (*i*) the soundness of the split of release accesses; and (*ii*) the correctness of the mapping in the absence of release accesses. The first obligation is solely on the side of IMM, and is formally presented next.

THEOREM 4.1. Let G be an IMM execution graph such that G.po;  $[G.W^{rel}] \subseteq G.po^?$ ;  $[G.F^{rel}]$ ;  $G.po \cup G.rmw$ . Let G' be the IMM execution graph obtained from G by weakening the access modes of release write events to a relaxed mode. Then, IMM-consistency of G' implies IMM-consistency of G.

Next, we establish the correctness of the mapping (in the absence of release writes) with respect to the model of the POWER architecture of Alglave et al. [2014], which we denote by POWER. As IMM, the POWER model is declarative, defining allowed outcomes via consistent execution graphs. Its labels are similar to IMM's labels (Def. 2.2) with the following exceptions:

- Read/write labels have the form R(x, v) and W(x, v): they do not include additional modes.

- There are three fence labels (listed here in increasing strength order): an "instruction fence" (F<sup>isync</sup>), a "lightweight fence" (F<sup>lwsync</sup>), and a "full fence" (F<sup>sync</sup>).

In turn, POWER execution graphs are defined as those of IMM (cf. Def. 2.3), except for the CAS dependency, casdep, which is not present in POWER executions. The next definition presents the correspondence between IMM execution graphs and their mapped POWER ones following the compilation scheme in Fig. 4.

Definition 4.2. Let G be an IMM execution graph with whole serial numbers ( $\operatorname{sn}[G.E] \subseteq \mathbb{N}$ ), such that  $G.W^{\operatorname{rel}} = \emptyset$ . A POWER execution graph  $G_p$  corresponds to G if the following hold:

- $G_p.E = G.E \cup \{\langle i, n + 0.5 \rangle \mid \langle i, n \rangle \in (G.R^{acq} \setminus dom(G.rmw)) \cup codom([G.R^{acq}]; G.rmw)\}$  (new events are added after acquire reads and acquire RMW pairs)

- $G_p.1ab = \{e \mapsto (G.1ab(e)) \mid e \in G.E\} \cup \{e \mapsto F^{isync} \mid e \in G_p.E \setminus G.E\}$  where:

- $G.rmw = G_p.rmw$ ,  $G.data = G_p.data$ , and  $G.addr = G_p.addr$  (the compilation does not change RMW pairs and data/address dependencies)

- $G.\mathsf{ctrl} \subseteq G_p.\mathsf{ctrl}$  (the compilation only adds control dependencies)

- $[G.R^{acq}]$ ;  $G.po \subseteq G_p.rmw \cup G_p.ctrl$ (a control dependency is placed from every acquire read)

- $[G.R_{ex}]$ ;  $G.po \subseteq G_p.ctrl \cup G_p.rmw \cap G_p.data$  (exclusive reads entail a control dependency to any future event, except for their immediate exclusive write successor if arose from an atomic increment)

- G.data; [codom(G.rmw)];  $G.po \subseteq G_p.ctrl$  (data dependency to an exclusive write entails a control dependency to any future event)

<sup>&</sup>lt;sup>7</sup>Since IMM does not have a primitive that corresponds to POWER's instruction fence, we cannot apply the same trick for acquire reads.

Bridging the Gap between Programming Languages and Hardware Weak Memory Models 69:15

Fig. 5. Compilation scheme from IMM to ARMv8.

G.casdep; G.po ⊆ G<sub>p</sub>.ctrl

(CAS dependency to an exclusive read entails a control dependency to any future event)

Next, we state our theorem that ensures IMM-consistency if the corresponding POWER execution graph is POWER-consistent. Due to lack of space, we do not include here the (quite elaborate) definition of POWER-consistency. For that definition, we refer the reader to [Alglave et al. 2014] (Appendix B provides the definition we used in our development).

THEOREM 4.3. Let G be an IMM execution graph with whole serial numbers  $(sn[G.E] \subseteq \mathbb{N})$ , such that  $G.W^{rel} = \emptyset$ , and let  $G_p$  be a POWER execution graph that corresponds to G. Then, POWER-consistency of  $G_p$  implies IMM-consistency of G.

The ARMv7 model in [Alglave et al. 2014] is very similar to the POWER model. There are only two differences. First, ARMv7 lacks an analogue for POWER's lightweight fence (lwsync). Second, ARMv7 has a weaker preserved program order than POWER, which in particular does not always include [G.R];  $G.\text{po}|_{G.\text{loc}}$ ; [G.W] (the  $\text{po}|_{\text{loc}}/\text{cc}$  rule is excluded, see Appendix B. In our proofs for POWER, however, we never rely on POWER's ppo, but rather assume the weaker one of ARMv7. The compilation schemes to ARMv7 are essentially the same as those to POWER substituting the corresponding ARMv7 instructions for the POWER ones: dmb instead of sync and lwsync, and isb instead of isync. Thus, the correctness of compilation to ARMv7 follows directly from the correctness of compilation to POWER.

#### 4.2 From IMM to ARMv8

The intended mapping of IMM to ARMv8 is presented schematically in Fig. 5. It is identical to the mapping to POWER (Fig. 4), except for the following:

- Unlike POWER, ARMv8 has machine instructions for acquire loads (ldar) and release stores (stlr), which are used instead of placing barriers next to plain loads and stores.

- ARMv8 has a special dmb.ld barrier that is used for IMM's acquire fences. On the other side, it lacks an analogue for IMM's release fence, for which a full barrier (dmb.sy) is used.

- As noted in Example 3.10, the mapping of IMM's strong RMWs requires placing a dmb.ld barrier after the exclusive write.

As a model of the ARMv8 architecture, we use its recent official declarative model [Deacon 2017] (see also [Pulte et al. 2018]) which we denote by ARM.<sup>8</sup> Its labels are given by:

- ARM read label:  $R^{o_R}(x, v)$  where  $x \in Loc, v \in Val$ , and  $o_R \in \{rlx, Q\}$ .

- ARM write label:  $W^{o_W}(x, v)$  where  $x \in Loc, v \in Val$ , and  $o_W \in \{rlx, L\}$ .

- ARM fence label:  $F^{o_F}$  where  $o_F \in \{1d, sy\}$ .

$<sup>^8 \</sup>text{We}$  only describe the fragment of the model that is needed for mapping of IMM, thus excluding sequentially consistent reads and i sb fences.

In turn, ARM's execution graphs are defined as IMM's ones, except for the CAS dependency, casdep, which is not present in ARM executions. As we did for POWER, we first interpret the intended compilation on execution graphs:

Definition 4.4. Let G be an IMM execution graph with whole serial numbers ( $\operatorname{sn}[G.E] \subseteq \mathbb{N}$ ). An ARM execution graph  $G_a$  corresponds to G if the following hold (we skip the explanation of conditions that appear in Def. 4.2):

- $G_a.E = G.E \cup \{\langle i, n + 0.5 \rangle \mid \langle i, n \rangle \in G.W_{strong}\}$  (new events are added after strong exclusive writes)

- $G_a.lab = \{e \mapsto (G.lab(e)) \mid e \in G.E\} \cup \{e \mapsto F^{ld} \mid e \in G_a.E \setminus G.E\}$  where:

$$\begin{array}{ll} (|\mathsf{R}^{\mathsf{rlx}}_s(x,\upsilon)|) \triangleq \mathsf{R}^{\mathsf{rlx}}(x,\upsilon) & (|\mathsf{W}^{\mathsf{rlx}}_{\mathsf{ORNW}}(x,\upsilon)|) \triangleq \mathsf{W}^{\mathsf{rlx}}(x,\upsilon) \\ (|\mathsf{R}^{\mathsf{acq}}_s(x,\upsilon)|) \triangleq \mathsf{R}^{\mathsf{Q}}(x,\upsilon) & (|\mathsf{W}^{\mathsf{rel}}_{\mathsf{ORNW}}(x,\upsilon)|) \triangleq \mathsf{W}^{\mathsf{L}}(x,\upsilon) \\ (|\mathsf{F}^{\mathsf{acq}}|) \triangleq \mathsf{F}^{\mathsf{ld}} & (|\mathsf{F}^{\mathsf{rel}}|) = (|\mathsf{F}^{\mathsf{acqrel}}|) = (|\mathsf{F}^{\mathsf{sc}}|) \triangleq \mathsf{F}^{\mathsf{sy}} \\ \end{array}$$

- $G.rmw = G_a.rmw$ ,  $G.data = G_a.data$ , and  $G.addr = G_a.addr$

- $G.\mathsf{ctrl} \subseteq G_a.\mathsf{ctrl}$

- $[G.R_{ex}]$ ;  $G.po \subseteq G_a.ctrl \cup G_a.rmw \cap G_a.data$

- G.casdep; G.po  $\subseteq G_a$ .ctrl

Next, we state our theorem that ensures IMM-consistency if the corresponding ARM execution graph is ARM-consistent. Again, due to lack of space, we do not include here the definition of ARM-consistency. For that definition, we refer the reader to [Deacon 2017; Pulte et al. 2018] (Appendix C provides the definition we used in our development).

THEOREM 4.5. Let G be an IMM execution graph with whole serial numbers ( $sn[G.E] \subseteq \mathbb{N}$ ), and let  $G_a$  be an ARM execution graph that corresponds to G. Then, ARM-consistency of  $G_a$  implies IMM-consistency of G.

# 5 FROM C11 AND RC11 TO IMM

In this section, we establish the correctness of the mapping from the C11 and RC11 models to IMM. Since C11 and RC11 are defined declaratively and IMM-consistency is very close to (R)C11-consistency, these results are straightforward.

Incorporating the fixes from Vafeiadis et al. [2015] and Lahav et al. [2017] to the original C11 model of Batty et al. [2011], and restricting attention to the fragment of C11 that has direct IMM counterparts (thus, excluding non-atomic and SC accesses), C11-consistency is defined follows.

*Definition 5.1. G* is called *C11-consistent* if the following hold:

- codom(G.rf) = G.R.

- For every location  $x \in Loc$ , G.co totally orders G.W(x).

- *G*.hb<sub>RC11</sub>; *G*.eco<sup>?</sup> is irreflexive.

- $G.rmw \cap (G.fre; G.coe) = \emptyset$ .

- $[F^{sc}]$ ;  $(hb_{RC11} \cup hb_{RC11}; eco; hb_{RC11})$ ;  $[F^{sc}]$  is acyclic.

It is easy to show that IMM-consistency implies C11-consistency, and consequently, the identity mapping is a correct compilation from this fragment of C11 to IMM. This result can be extended to include non-atomic and SC accesses as follows:

Non-atomic accesses provide weaker guarantees than relaxed accesses, and are not needed for

accounting for IMM's behaviors. Put differently, one may assume that the compilation from C11

to IMM first strengthens all non-atomic accesses to relaxed accesses. Compilation correctness

then follows from the soundness of this strengthening and our result that excludes non-atomics.

• The semantics of SC accesses in C11 was shown to be too strong in [Lahav et al. 2017; Manerkar et al. 2016] to allow the intended compilation to POWER and ARMv7. If one applies the fix proposed in [Lahav et al. 2017], then compilation correctness could be established following their reduction, that showed that it is sound to globally split SC accesses to SC fences and release/acquire accesses on the source level. This encoding yields the (two) expected compilation schemes for SC loads and stores on x86, ARMv7, and POWER. On the other hand, handling ARMv8's specific instructions for SC accesses is left for future work. We note that the usefulness and the "right semantics" for SC accesses is still under discussion. The Promising semantics, for instance, does not have primitive SC accesses at all and implements them using SC fences.

In turn, RC11 (ignoring the part related to SC accesses) is obtained by strengthening Def. 5.1 with a condition asserting that  $G.po \cup G.rf$  is acyclic. To enforce the additional requirement, the mapping of RC11 places a (control) dependency or a fence between every relaxed read and subsequent relaxed write. It is then straightforward to define the correspondence between source (RC11) execution graphs and target (IMM) ones, and prove that IMM-consistency of the target graph implies RC11-consistency of the source. This establishes the correctness of the intended mapping from RC11 without non-atomic accesses to IMM. Handling non-atomic accesses, which are intended to be mapped to plain machine accesses with no additional barriers or dependencies (on which IMM generally allows po  $\cup$  rf-cycles), is left for future work; while SC accesses can be handled as mentioned above.

#### 6 FROM THE PROMISING SEMANTICS TO IMM: RELAXED FRAGMENT

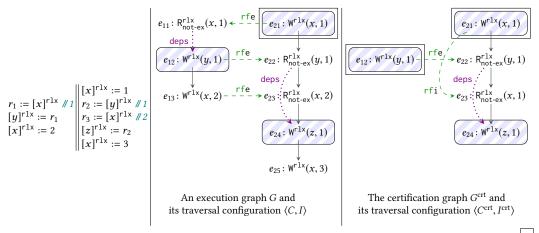

In the section, we outline the main ideas of the proof of the correctness of compilation from the promising semantics of Kang et al. [2017], denoted by Promise, to IMM. To assist the reader, we initially restrict attention to programs containing only relaxed read and write accesses. In §7, we show how to adapt and extend our proof to the full model.

Our goal is to prove that for every outcome of a program prog (with relaxed accesses only) under IMM (Def. 2.9), there exists a Promise trace of prog terminating with the same outcome. To do so, we introduce a traversal strategy of IMM-consistent execution graphs, and show, by forward simulation argument, that it can be followed by Promise. The main challenge in the simulation proof is due to the certification requirement of Promise—after every step, the thread that made the transition has to show that it can run in isolation and fulfill all its so-called promises. To address this challenge, we break our simulation argument into two parts. First, we provide a simulation relation, which relates a Promise thread state with a traversal configuration. Second, after each traversal step, we (i) construct a certification execution configuration and a new traversal configuration configuration

The rest of this section is structured as follows. In  $\S6.1$  we describe the fragment of Promise restricted to relaxed accesses. In  $\S6.2$  we introduce the traversal of IMM-consistent execution graphs, which is suitable for the relaxed fragment. In  $\S6.3$  we define the simulation relation for Promise thread steps and the execution graph traversal. In  $\S6.4$  we discuss how we handle certification. Finally, in  $\S6.5$  we state the compilation correctness theorem and provide its proof outline.

# 6.1 The Promise Machine (Relaxed Fragment)

Promise is an operational model where threads execute in an interleaved fashion. The *machine* state is a pair  $\Sigma = \langle TS, M \rangle$ , where TS assigns a thread state TS to every thread and M is a (global) memory. The memory consists of a set of messages of the form  $\langle x : v@t \rangle$  representing all previously

executed writes, where  $x \in \text{Loc}$  is the target location,  $v \in \text{Val}$  is the stored value, and  $t \in \mathbb{Q}$  is the *timestamp*. The timestamps totally order the messages to each location (this order corresponds to G.co in our simulation proof).

The state of each thread contains a *thread view*,  $\mathcal{V} \in \text{View} \triangleq \text{Loc} \rightarrow \mathbb{Q}$ , which represents the "knowledge" of each thread. The view is used to forbid a thread to read from a (stale) message  $\langle x : v@t \rangle$  if it is aware of a newer one, *i.e.*, when  $\mathcal{V}(x)$  is greater than t. Also, it disallows to write a message to the memory with a timestamp not greater than  $\mathcal{V}(x)$ . (Due to lack of space, we refer the reader to Kang et al. [2017] for the full definition of thread steps.)

Besides the step-by-step execution of their programs, threads may non-deterministically *promise* future writes. This is done by simply adding a message to the memory. We refer to the execution of a write instruction whose message was promised before as *fulfilling* the promise.

The *thread state TS* is a triple  $\langle \sigma, \mathcal{V}, P \rangle$ , where  $\sigma$  is the thread's local state,  $\mathcal{V}$  is the thread view, and P tracks the set of messages that were promised by the thread and not yet fulfilled. We write TS.prm to obtain the promise set of a thread state TS. Initially, each thread is in local state  $TS_0^i = \langle \sigma_0(prog(i)), \lambda x. 0, \emptyset \rangle$ .

To ensure that promises do not make the semantics overly weak, each sequence of thread steps in Promise has to be *certified*: the thread that took the steps should be able to fulfill all its promises when executed in isolation. Thus, a *machine step* in Promise is given by:

$$\frac{\langle \mathcal{TS}(i), M \rangle \to^+ \langle \mathit{TS}', M' \rangle \qquad \exists \mathit{TS}''. \ \langle \mathit{TS}', M' \rangle \to^* \langle \mathit{TS}'', \_ \rangle \land \mathit{TS}''.\mathsf{prm} = \emptyset}{\langle \mathcal{TS}, M \rangle \to \langle \mathcal{TS}[i \mapsto \mathit{TS}'], M' \rangle}$$

Program outcomes under Promise are defined as follows.

Definition 6.1. A function  $O: \mathsf{Loc} \to \mathsf{Val}$  is an *outcome* of a program *prog* under Promise if  $\Sigma_0(prog) \to^* \langle \mathcal{TS}, M \rangle$  for some  $\mathcal{TS}$  and M such that the thread's local state in  $\mathcal{TS}(i)$  is terminal for every  $i \in \mathsf{Tid}$ , and for every  $x \in \mathsf{Loc}$ , there exists a message of the form  $\langle x : O(x)@t \rangle \in M$  where t is maximal among timestamps of messages to x in M. Here,  $\Sigma_0(prog)$  denotes the initial machine state,  $\langle \mathcal{TS}_{\mathrm{init}}, M_{\mathrm{init}} \rangle$ , where  $\mathcal{TS}_{\mathrm{init}} = \lambda i$ .  $TS_0^i$ , and  $M_{\mathrm{init}} = \{\langle x : 0@0 \rangle \mid x \in \mathsf{Loc} \}$ .

Example 6.2 (Load Buffering). Consider the following load buffering behavior under IMM:

The Promise machine obtains this outcome as follows. Starting with memory  $\langle \langle x:0@0\rangle, \langle y:0@0\rangle\rangle$ , the left thread promises the message  $\langle y:1@1\rangle$ . After that, the right thread reads this message and executes its second instruction (promises a write and immediately fulfills it), adding the the message  $\langle x:1@1\rangle$  to memory. Then, the left thread reads from that message and fulfills its promise. Each step (including, in particular, the first promise step) could be easily "certified" in a thread-local execution. Note also how the data dependency in the right thread redistrict the execution of the Promise machine. Due to the certification requirement, the execution cannot begin by the right thread promising  $\langle x:1@1\rangle$ , as it cannot generate this message by running in isolation.

#### 6.2 Traversal (Relaxed Fragment)

Our goal is to generate a run of Promise for any given IMM-consistent initialized execution graph G of a program prog. To do so, we traverse G with a certain strategy, deciding in each step whether

$<sup>^9</sup>$ The promising semantics is generally formulated over a general labeled state transition system. In our development, we instantiate it with the sequential program semantics that is used in  $\S 2.3$  to construct execution graphs.

to execute the next instruction in the program or promise a future write. While traversing G, we keep track of a *traversal configuration*—a pair  $TC = \langle C, I \rangle$  of subsets of G.E. We call the events in C and I covered and issued respectively. The covered events correspond to the instructions that were executed by Promise, and the issued events correspond to messages that were added to the memory (executed or promised stores).

Initially, we take  $TC_0 = \langle G.E \cap Init, G.E \cap Init \rangle$ . Then, at each traversal step, the covered and/or issued sets are increased, using one of the following two steps:

$$(ISSUE) \qquad (COVER) \\ \hline w \in Issuable(G, C, I) \qquad e \in Coverable(G, C, I) \\ \hline G \vdash \langle C, I \rangle \rightarrow_{tid(w)} \langle C, I \uplus \{w\} \rangle \qquad G \vdash \langle C, I \rangle \rightarrow_{tid(e)} \langle C \uplus \{e\}, I \rangle$$

The (ISSUE) step adds an event *w* to the issued set. It corresponds to a promise step of Promise. We require that *w* is issuable, which says that all the writes of other threads that it depends on have already been issued:

Definition 6.3. An event w is issuable in G and  $\langle C, I \rangle$ , denoted  $w \in \mathsf{Issuable}(G, C, I)$ , if  $w \in G.W$  and  $dom(G.\mathsf{rfe}; G.\mathsf{ppo}; [w]) \subseteq I$ .

The (COVER) step adds an event e to the covered set. It corresponds to an execution of a program instruction in Promise. We require that e is coverable, as defined next.

*Definition 6.4.* An event *e* is called *coverable* in *G* and  $\langle C, I \rangle$ , denoted *e* ∈ Coverable(*G*, *C*, *I*), if  $e \in G.E$ ,  $dom(G.po; [e]) \subseteq C$ , and either (*i*)  $e \in G.W \cap I$ ; or (*ii*)  $e \in G.R$  and  $dom(G.rf; [e]) \subseteq I$ .

The requirements in this definition are straightforward. First, all *G*.po-previous events have to be covered, *i.e.*, previous instructions have to be already executed by Promise. Second, if *e* is a write event, then it has to be already issued; and if *e* is a read event, then the write event that *e* reads from has to be already issued (the corresponding message has to be available in the memory).

As an example of a traversal, consider the execution from Example 6.2. A possible traversal of the execution is the following: issue  $e_{12}$ , cover  $e_{21}$ , issue  $e_{22}$ , cover  $e_{22}$ , cover  $e_{11}$ , and cover  $e_{12}$ .

Starting from the initial configuration  $TC_0$ , each traversal step maintains the following invariants: (i)  $E \cap \text{Init} \subseteq C$ ; (ii)  $C \cap G.W \subseteq I$ ; and (iii)  $I \subseteq \text{Issuable}(G, C, I)$  and  $C \subseteq \text{Coverable}(G, C, I)$ . When these properties hold, we say that  $\langle C, I \rangle$  is a *traversal configuration* of G. The next proposition ensures the existence of a traversal starting from any traversal configuration. (A proof outline for an extended version of the traversal discussed in §7.2 is presented in Appendix F.)

PROPOSITION 6.5. Let G be an IMM-consistent execution graph and  $\langle C, I \rangle$  be a traversal configuration of G. Then,  $G \vdash \langle C, I \rangle \rightarrow^* \langle G.E, G.W \rangle$ .

## 6.3 Thread Step Simulation (Relaxed Fragment)

To show that a traversal step of thread i can be matched by a Promise thread step, we use a simulation relation  $I_i(G, TC, \langle TS, M \rangle, T)$ , where G is an IMM-consistent initialized full execution of P of P is a traversal configuration of P is P is P is P is thread state in Promise; P is the memory of Promise; and P is a function that assigns timestamps to issued writes. The relation P is P is the following conditions are met (for conciseness we omit the "P of P or P is thread state in Promise; P is the memory of Promise; and P is a function that assigns timestamps to issued writes.

- (1) T agrees with co:

- $\forall w \in E \cap Init. T(w) = 0$

- $\forall \langle w, w' \rangle \in [I]$ ; co; [I].  $T(w) \leq T(w')$

- (2) Non-initialization messages in *M* have counterparts in *I*:

Fig. 6. A program, its execution graph, and a related certification graph. Covered events are marked by and issued ones by .

- $\forall \langle x : \underline{@}t \rangle \in M. \ t \neq 0 \Rightarrow \exists w \in I. \ loc(w) = x \land T(w) = t$

- (3) Issued events have corresponding messages in memory:

- $\forall w \in I. \langle loc(w) : val(w)@T(w) \rangle \in M$

- (4) For every promise, there exists a corresponding issued uncovered event w:

- $\forall \langle x : v@t \rangle \in P$ .  $\exists w \in E_i \cap I \setminus C$ .  $loc(w) = x \land val(w) = v \land T(w) = t$

- (5) Every issued uncovered event w of thread i has a corresponding promise in P.

- $\forall w \in E_i \cap I \setminus C$ .  $\langle loc(w) : val(w)@T(w) \rangle \in P$

- (6) The view V is justified by graph paths:

- $\mathcal{V} = \lambda x$ . max  $T[W(x) \cap dom(vf_{rlx}; [E_i \cap C])]$  where  $vf_{rlx} \triangleq rf^?; po^?$

- (7) The thread local state  $\sigma$  matches the covered events ( $\sigma$ .G.E =  $C \cap E_i$ ), and can always reach the execution graph G ( $\exists \sigma'$ .  $\sigma \to_i^* \sigma' \land \sigma'$ .G =  $G|_i$ ).

PROPOSITION 6.6. If  $I_i(G, TC, \langle TS, M \rangle, T)$  and  $G \vdash TC \rightarrow_i TC'$  hold, then there exist TS', M', T' such that  $\langle TS, M \rangle \rightarrow \langle TS', M' \rangle$  and  $I_i(G, TC', \langle TS', M' \rangle, T')$  hold.

In addition, it is easy to verify that the initial states are related, *i.e.*,  $I_i(G, TC_0, \langle TS_0^i, M_{\text{init}} \rangle, \bot)$  holds for every  $i \in \text{Tid}$ .

#### 6.4 Certification (Relaxed Fragment)